División entera positiva.

235 views

Skip to first unread message

Democrito

Feb 16, 2021, 8:28:14 PM2/16/21

to FPGAwars: explorando el lado libre

Hola,

Quien haya visto el circuito de este hilo habrá comprobado que para dividir en coma o punto fijo necesito dividir con resultado entero. No es que tenga que ser así, pero el algoritmo que he utilizado lo necesita. El problema está que si le pedimos al sintetizador que nos haga una división entera para dos números cualquiera consume bastantes recursos.

Para ello he utilizado el método de sumas sucesivas en vez de restas, el método es muy similar. En vez de ir restando el divisor al dividendo y esperar llegar a 0 o negativo, voy sumando el divisor sucesivamente hasta alcanzar o sobrepasar al dividendo.

El diseño tiene presente 0/0 y n/0, producirá una señal (tic) de error y el cociente siempre será 0 en estos casos.

Para quien sienta interés o lo necesite dejo este enlace a mi Github:

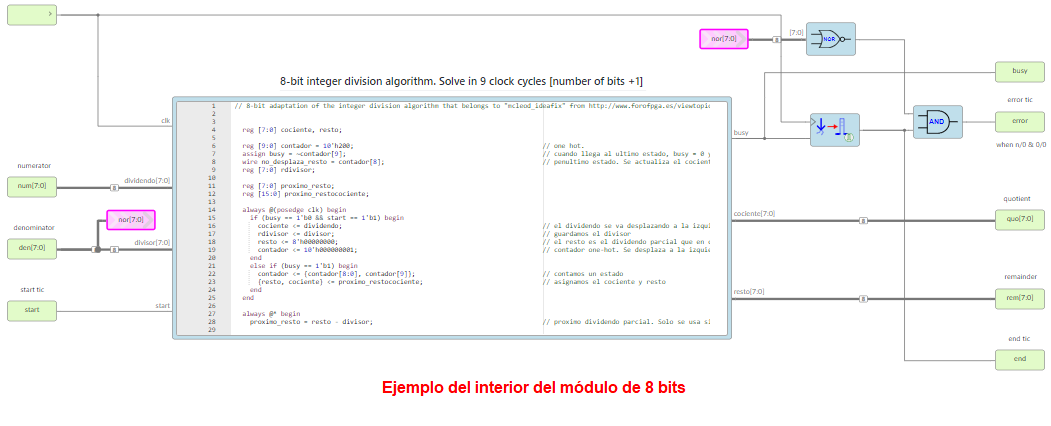

Y tengo probado otra forma más eficiente de hacer estas divisiones enteras, donde consume menos recursos, la velocidad máxima de reloj es más alta, y realiza la operación en unos pocos ciclos (número de bits utilizados + 1). Además de dar el cociente también da el resto. Será en cajitas de código en verilog para Icestudio, con tres versiones: 8, 16 y 32 bits. Durante esta semana creo que lo sacaré. Este algoritmo no es mío y cuando lo publique pondré de dónde lo he sacado.

Saludos.

charli va

Feb 17, 2021, 12:22:49 AM2/17/21

to fpga-wars-explora...@googlegroups.com

Hola Demócrito ¿tienes pensado ahcer alguna colección de matemáticas? te lo digo porque si no lo vas a hacer , estaría genial crear en FPGAwars una colección y que cuando los tengas ir subiendo todos estos bloques.

En general el tema de que se pierda todo en hilos de la lista es algo que me preocupa bastante, hay un montón de cosas que están perdidas en el tiempo y de vez en cuando afloran y es como....WTF!

Ya nos contarás, parece todo muy interesante y prometedor!! hasta la ALU y más allá!! :)

--

Has recibido este mensaje porque estás suscrito al grupo "FPGAwars: explorando el lado libre" de Grupos de Google.

Para cancelar la suscripción a este grupo y dejar de recibir sus mensajes, envía un correo electrónico a fpga-wars-explorando-el...@googlegroups.com.

Para ver esta conversación en el sitio web, visita https://groups.google.com/d/msgid/fpga-wars-explorando-el-lado-libre/f085ed37-5305-430a-965e-529a7c97cc1en%40googlegroups.com.

Democrito

Feb 17, 2021, 4:27:57 AM2/17/21

to FPGAwars: explorando el lado libre

Hola Charli!

Si no he metido en la hoja de cálculo que pusiste en Internet para una futura biblioteca el módulo de división entera se debe a que como comenté hay otra forma más eficiente de dividir enteros positivos, y esos sí los subiré a tu hoja. Cuando lo descubrí ya había casi terminado lo de "sumas sucesivas que funciona como restas sucesivas", pero quería terminarlo como reto (estaba resolviendo lo de 0/0 y n/0 hasta ayer). El nuevo método le queda pendiente precisamente eso (0/0 y n/0) aunque creo que hay un modo de resolverlo relativamente sencillo.

Por otra parte quiero evitar poner dos versiones de una misma cosa porque podría confundir sin información de antemano. Por eso lo de restas sucesivas (o sumas) lo dejo como anécdota, ya que es mucho menos eficiente.

Sobre el "I2C genérico" lo he dejado aparcado porque tiene mucha tela pero quiero volver a él en cuando el "Síndrome del Ansia Viva" sobre los algoritmos me baje un poco. La intención es esa, que poco a poco vaya creando una biblioteca de operaciones básicas para poder hacer un poco de matemáticas. Un poco de trigonometría, raíces cuadradas, divisiones, y lo que surja.

Muchas gracias por tu trabajo y que todos nos beneficiamos!

Saludos!

charli va

Feb 17, 2021, 4:41:05 AM2/17/21

to fpga-wars-explora...@googlegroups.com

Genial Demócrito!! y gracias por los ánimos como siempre digo yo lo hago encantado !

Como ya te digo ando "obsesionado" con como organizar todo lo que se está generando y sobre todo que tenga visibilidad, y estoy pensando en varias cosas, a ver si vamos quitándonos marrones que ahora ando con una mejora bastante importante de icestudio y que me está consumiendo el tiempo para otras cosas.

Y por lo de tener cosas aparcadas.... como siempre ni te preocupes, creo que esta lista es un "grupo de mochileros" que vmos siempre con las mochilas hasta arriba.

¡Un abrazo!

--

Has recibido este mensaje porque estás suscrito al grupo "FPGAwars: explorando el lado libre" de Grupos de Google.

Para cancelar la suscripción a este grupo y dejar de recibir sus mensajes, envía un correo electrónico a fpga-wars-explorando-el...@googlegroups.com.

Para ver esta conversación en el sitio web, visita https://groups.google.com/d/msgid/fpga-wars-explorando-el-lado-libre/cfa880ce-4f6e-47e4-b31d-bad07e91cd39n%40googlegroups.com.

Democrito

Feb 21, 2021, 5:01:15 PM2/21/21

to FPGAwars: explorando el lado libre

Hola de nuevo,

Ya he terminado los 3 bloques (8, 16 y 32 bits) con dos ejemplos sencillos de la nueva división entera que es muy eficiente. Utiliza número de bits + 1 ciclos de reloj para dar el resultado, tanto del cociente como del resto.

Lo de "número de ciclos +1" significa que si es de 8 bits utilizará 9 ciclos de reloj, si es de 16 bits utilizará 17 ciclos de reloj, y si es de 32 bits utilizará 33 ciclos de reloj.

El algoritmo en verilog lo he sacado de este foro: http://www.forofpga.es/viewtopic.php?t=288 pertenece a un tal "mcleod_ideafix". Originalmente el algoritmo es de 32 bits y lo adapté para que funcionase también para 8 y 16 bits. Le añadí la señal de error (salida tipo tic) que sólo se producirá si dividimos un número entre 0.

El algoritmo ocupa poco espacio, es muy eficiente y trabaja a una buena frecuencia de reloj.

Los bloques principales y dos ejemplos los podéis descarga desde mi Github: https://github.com/Democrito/repositorios/tree/master/Maths/div_uint

También he añadido los tres módulos a la hoja de cálculo de Carlos.

Saludos.

Democrito

Feb 21, 2021, 5:13:17 PM2/21/21

to FPGAwars: explorando el lado libre

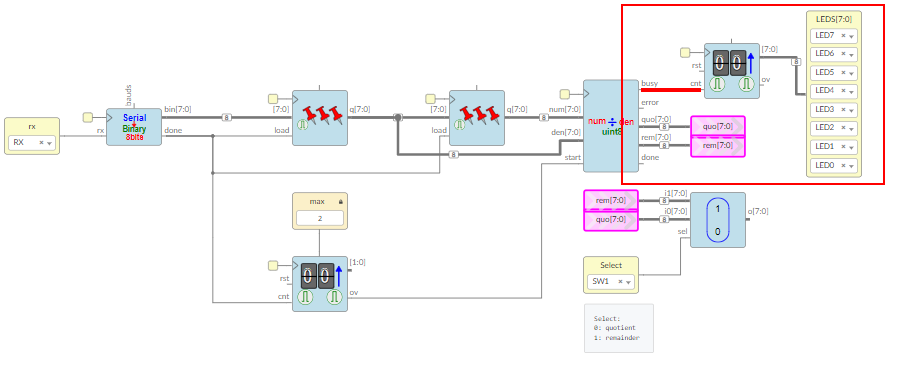

Una forma súper sencilla de comprobar cuántos ciclos de reloj consume es poniendo un contador de 8 bits (con sus respectivos leds) conectado a "busy" (la entrada del contador a busy). Mientras esa patilla esté a 1 irá contando los ciclos de reloj. Al terminar podemos leer en los leds los ciclos consumidos.

Este es un ejemplo realizado en el ejemplo de división de 8 bits.

Alberto Martin

Feb 22, 2021, 10:51:23 AM2/22/21

to fpga-wars-explora...@googlegroups.com

Hola soy José hermano de Alberto Martín que falleció el día 31 de enero gracias por todo

--

Has recibido este mensaje porque estás suscrito al grupo "FPGAwars: explorando el lado libre" de Grupos de Google.

Para cancelar la suscripción a este grupo y dejar de recibir sus mensajes, envía un correo electrónico a fpga-wars-explorando-el...@googlegroups.com.

Para ver esta conversación en el sitio web, visita https://groups.google.com/d/msgid/fpga-wars-explorando-el-lado-libre/0227041f-2b37-47c8-823c-342db200bc1en%40googlegroups.com.

Reply all

Reply to author

Forward

0 new messages