División en coma o punto fijo

409 views

Skip to first unread message

Democrito

Feb 1, 2021, 10:28:34 PM2/1/21

to FPGAwars: explorando el lado libre

Hola,

Estoy estudiando y a la vez trabajando la comprensión de números en coma fija (o punto fijo para los anglo-parlantes).

Este tema es bastante complejo de explicar y más adelante documentaré todo esto, aunque aún me queda mucho por aprender por tanto tardaré en hacerlo. Con programación he conseguido hacer un CORDIC de senos y cosenos. Cuando consiga los conocimientos suficientes trataré de sacar un CORDIC para senos, cosenos y atan2 para la FPGA. Las matemáticas pueden dar un potencial enorme a proyectos complejos con FPGA.

Sólo quería mostraros por dónde voy de momento con FPGA. Se trata de dividir dos números enteros positivos y poder ver el resultado en el terminal serie en formato coma fija (o punto fijo). Este formato no es tan exacto como el punto flotante, pero puede ser muy útil para proyectos que impliquen una física en la que no acumulamos errores.

El ICE que adjunto está en plan.... vamos que da pena, y está al límite de los 12 MHz que trabaja la Alhambra (me sale 12.22 MHz).

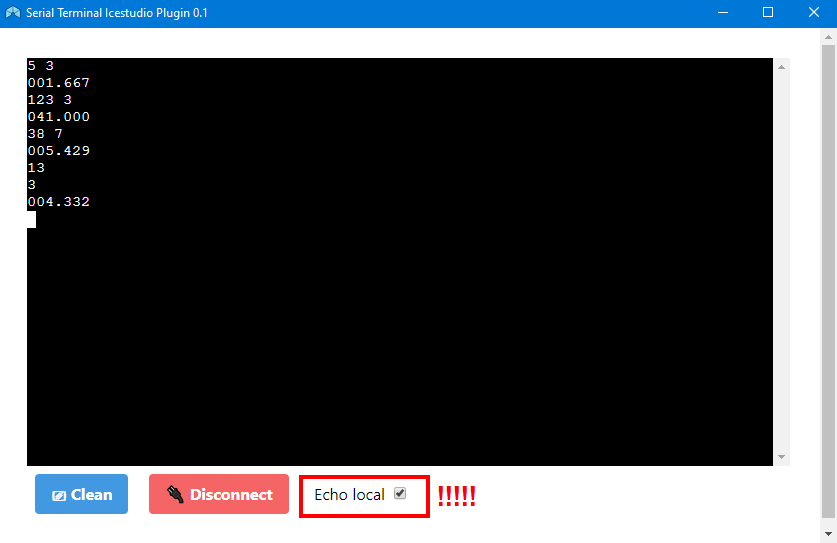

La forma de hacerlo funcionar es muy simple, le metes un número de rango 0...255 pulsas espacio o coma o enter, y después le metes otro número de la misma manera y al pulsar enter (o espacio o coma) te saldrá el resultado de la operación.

Se puede utilizar cualquier terminal serial (el de Arduino por ejemplo) aunque yo casi siempre uso el terminal del propio Icestudio. En este terminal serie activa el "Echo local" para poder ver la introducción de los números, por eso lo he enfatizado y puesto en rojo.

Adjunto ICE.

Un saludo.

Democrito

Feb 1, 2021, 10:56:14 PM2/1/21

to FPGAwars: explorando el lado libre

Vuelvo a adjuntar el ICE con unas correcciones en la caja de código donde se hace la división.

Si os fijáis en los recursos consume 1278 Luts. Hay que tener en cuenta que hay un emisor y receptor serie, dos conversores de binario a ASCII especiales que pueden convertir números 0..999 y está hecho a base de doble contadores con sumadores de 8 bits en cada dígito... y luego las dos máquinas de contar... Total, que para hacer cálculos en realidad no usa tantos recursos, sino que se los come "los medio de transferencia y conversión".

Democrito

Feb 27, 2021, 3:43:22 PM2/27/21

to FPGAwars: explorando el lado libre

Hola,

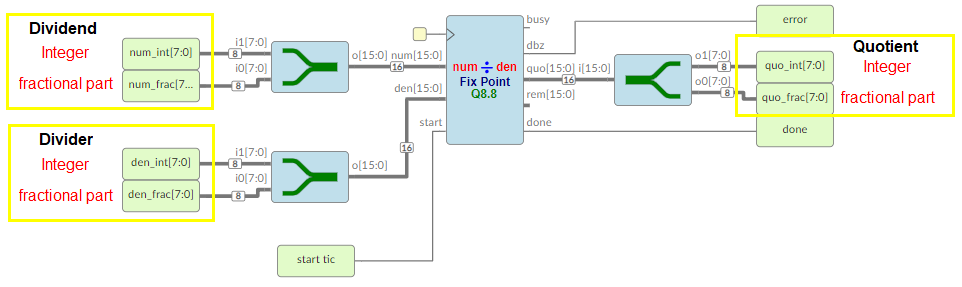

Estoy por la labor de ir fabricando módulos que nos permitan hacer operaciones matemáticas básicas, como en este caso la división con decimales. La división con decimales en punto fijo se llama Qint.frac, donde 'int' representa la parte entera y 'frac' representa la parte fraccionaria (los decimales).

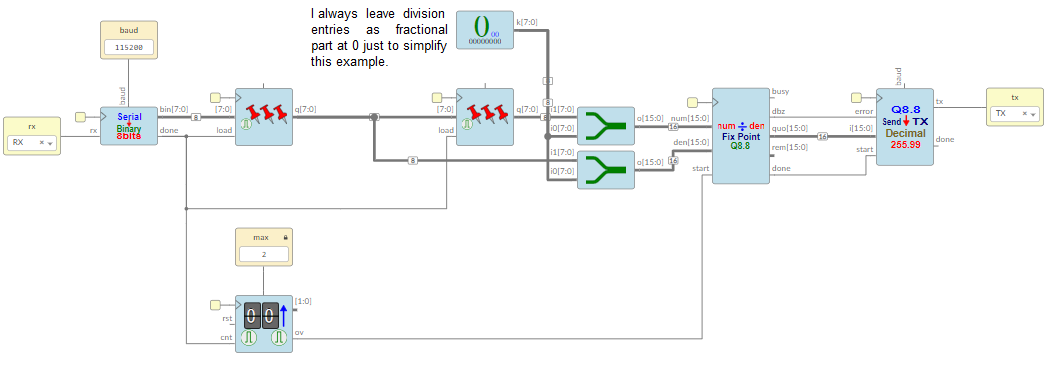

En este post adjunto un circuito donde utilizo para dividir con decimales el formato Q8.8. Esto significa que utilizo 8 bits para la parte entera y otros 8 bits como parte fraccionaria. Siempre hay que utilizar números positivos, de momento no se puede introducir números negativos.

Es decir, que podemos dividir con decimales y el resultado también nos dará decimales. La salida "dbz" se pondrá a 1 si ocurre una división entre 0.

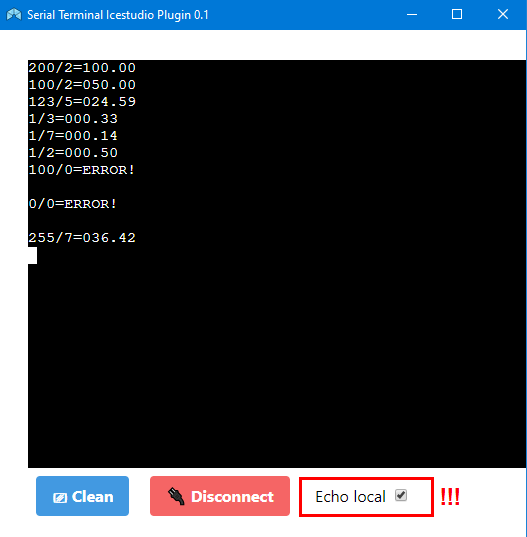

Como ejemplo he creado otro módulo donde traduce el formato Q8.8 a decimal de toda la vida y que podremos ver el resultado a través del puerto serie. Como estamos en formato Q8.8 el número más alto que se puede introducir es el 255, lo mismo para la parte fraccionaria, aunque en este último caso, para simplificar el ejemplo, la parte fraccionaria de entrada siempre la dejo con valor 0. Pero he hecho pruebas a parte y también divide con entradas fraccionarias (es decir, con decimales) sin problemas.

Si cargamos el circuito y abrimos el terminal serie de Icestudio podremos ver pruebas como esta:

Con tiempo iré creando otro módulos de división para Icestudio, tipo Q16.10 que nos permitirá enviar números de 0 al 65535 con parte fraccionaria que nos permita tener decimales hasta .999.

El módulo de división, en su interior hay un diseño hecho en Verilog. La división (sea cual sea) siempre se realizará con 24 ciclos de reloj. El algoritmo pertenece a Will Green y esta persona tiene una web alucinante sobre diseño en Verilog con proyectos geniales (también para gráficos) y os animo a visitar su web y daros un buen paseo. Yo estuve horas admirando todo su trabajo: https://projectf.io/ En concreto, la división con punto fijo y para cualquier anchura de bits se encuentra aquí: https://projectf.io/posts/division-in-verilog/

Adjunto el módulo y el ejemplo.

Saludos.

Democrito

Feb 27, 2021, 7:40:17 PM2/27/21

to FPGAwars: explorando el lado libre

Hace un rato he terminado el módulo que divide en formato Q16.16 y ejemplo respectivo.

Sólo ha sido ampliar y tocar allí y allá en el ejemplo para esta versión. Dicho ejemplo no puede traducir a BCD más allá de 999 (es un conversor interno que hay en el ejemplo), por tanto las divisiones que hagamos el resultado ha de ser menor que ese número.

Adjunto módulo y ejemplo para este ancho de bits.

Saludos.

charli va

Feb 28, 2021, 11:46:17 AM2/28/21

to fpga-wars-explora...@googlegroups.com

Muchas gracias Demócrito! el tema de punto fijo lo iba a mirar en breve para utilizarlo en un proyecto que tengo entre manos y me has ahorrado muchísimo trabajo , gracias por el curro y las referencias.

¡Un gran abrazo!!

--

Has recibido este mensaje porque estás suscrito al grupo "FPGAwars: explorando el lado libre" de Grupos de Google.

Para cancelar la suscripción a este grupo y dejar de recibir sus mensajes, envía un correo electrónico a fpga-wars-explorando-el...@googlegroups.com.

Para ver esta conversación en el sitio web, visita https://groups.google.com/d/msgid/fpga-wars-explorando-el-lado-libre/c1e5756c-48ad-42f2-9a64-795020598a93n%40googlegroups.com.

Democrito

Feb 28, 2021, 2:26:44 PM2/28/21

to FPGAwars: explorando el lado libre

Un placer siempre!

Leí o escuché por ahí que el juego Doom para poder trabajar en un 386 necesitaba una manera ligera de hacer cálculos y utilizaba el punto fijo.

Dejo un vídeo puesto en el momento que se habla de punto fijo, sólo son unos minutos dentro de un vídeo largo, pero se trata de la explicación que da.

Un abrazo fuerte para ti!

Obijuan

Mar 1, 2021, 1:17:08 PM3/1/21

to FPGAwars: explorando el lado libre

¡Qué gran aportación Demócrito! ¡Muchísimas gracias! 😀️

En la lista de tareas también tengo pendiente esta parte de punto fijo. Me a ser super útil. ¡Gracias!

Saludos, Obijuan

Democrito

Mar 1, 2021, 5:01:15 PM3/1/21

to FPGAwars: explorando el lado libre

Obijuan, me siento como un niño redescubriendo cierto tipo de cimientos que hicieron otros hace muchos años; es un darse cuenta cómo distintas personas, cada uno/a aportando su granito de arena, nos ha llevado hasta aquí.

Agradezco enormemente el trabajo que estáis haciendo Carlos y tu para que este tipo de cosas sucedan, ya se directa o indirectamente.

Gracias, de verdad.

charli va

Mar 1, 2021, 5:21:32 PM3/1/21

to fpga-wars-explora...@googlegroups.com

Gracias a ti Demócrito.

a ti y a todas las personas que aportan buena onda, críticas constructivas y desarrollos a esta comunidad, es lo que hace que todo esto tenga sentido.

Gracias de verdad!

Democrito

Dec 11, 2021, 6:21:40 PM12/11/21

to FPGAwars: explorando el lado libre

Hola,

Este mensaje es sólo comentar cosas que he separado y un ejemplo que he actualizado (tenía un limitación y no daba todo el rango y ahora sí) y optimizado.

Si alguien está interesado en representar a través del serial en "punto fijo" con formatos Q8.8 y Q16.16, puede descargarse los módulos para este menester aquí:

Y si alguien quiere probar un ejemplo práctico de división con decimales puede ir aquí:

El ejemplo donde se utiliza el formato Q16.16 está actualizado y ahora permite mostrar todo el rango, es decir que la parte entera puede tener el valor máximo de 65535, y el valor máximo de la parte decimal es de "punto" 9999

Saludos.

Jo mo

Dec 12, 2021, 2:40:05 AM12/12/21

to FPGAwars: explorando el lado libre

Hola Democrito,

Thanks a lot for all these Math block. i think missed that thread !

i profit from your, message to rise the question of the pertinence off adding your Math blocks in the iceArith collection. maybe in a " fixed point" subdirectory ?

Also ObiJuan, do you think we can join the two collection "IceArith" and "Icestudio-ArithmeticsBlocks in a single one (everything in IceArith)?

I can give a hand on that "block organising task"!

Kind regards and have a nice Sunday guys

Joaquim

Democrito

Dec 12, 2021, 8:53:51 AM12/12/21

to FPGAwars: explorando el lado libre

Hello Joaquim, good afternoon,

For my part, I would be delighted if all this was organized, or rather centralized in a common place. You have to ask Obijuan and Carlos if they already had something in mind. Organizing is laborious and if you wanted to do it, that's fine by me.

For my part, I would be delighted if all this was organized, or rather centralized in a common place. You have to ask Obijuan and Carlos if they already had something in mind. Organizing is laborious and if you wanted to do it, that's fine by me.

I have updated the information that I put above: https://github.com/Demoierto/repositorios/tree/master/Maths/div_fix_point

Have a nice afternoon!

Democrito

Dec 12, 2021, 8:56:45 AM12/12/21

to FPGAwars: explorando el lado libre

The previous link is broken, this one does not: https://github.com/Democrito/repositorios/tree/master/Maths/div_fix_point

Juan Gonzalez Gomez

Dec 12, 2021, 9:25:04 AM12/12/21

to FPGA-WARS: explorando el lado libre

Yes for sure!

It's ok for me to join the two collections. Later, when everything is organized, if the collection is too big we can split into different sub-collections. But for now, It makes a lot of sense to have all in the iceArith collection

I am currently focused on the iceIO collection: adding more blocks, examples, translations and documentation

Obijuan

--

Has recibido este mensaje porque estás suscrito al grupo "FPGAwars: explorando el lado libre" de Grupos de Google.

Para cancelar la suscripción a este grupo y dejar de recibir sus mensajes, envía un correo electrónico a fpga-wars-explorando-el...@googlegroups.com.

Para ver esta conversación en el sitio web, visita https://groups.google.com/d/msgid/fpga-wars-explorando-el-lado-libre/1eae22ee-6c0d-4d87-9929-d68b863f2720n%40googlegroups.com.

charli va

Dec 12, 2021, 1:29:46 PM12/12/21

to fpga-wars-explora...@googlegroups.com

Thanks a lot Democrito!,

Para ver esta conversación en el sitio web, visita https://groups.google.com/d/msgid/fpga-wars-explorando-el-lado-libre/CABqu7xpkWUMocwjJB1aYDuopB-atdo2KPjnTwm9e2zOFdcWFwA%40mail.gmail.com.

Jo mo

Dec 12, 2021, 7:38:13 PM12/12/21

to FPGAwars: explorando el lado libre

Ok, i will try to see if i can organize a bit iceArith collection as we discussed and pull request that.

@ Democrito, maybe we can add in your 2 block and 2 examples the link

https://github.com/Democrito/repositorios/tree/master/Maths/div_fix_point

At the place or just above the link you already put in you ice files.?

Something like that in the ice files.

Thanks

Joaquim

Democrito

Dec 12, 2021, 9:13:58 PM12/12/21

to FPGAwars: explorando el lado libre

Let time pass, now there are other priorities. Let's take some time and address this issue later. Everything will come in due time. And your availability is greatly appreciated.

limena limena

Dec 13, 2021, 12:04:31 AM12/13/21

to fpga-wars-explora...@googlegroups.com

Es un buen trabajo. Enhorabuena

Para ver esta conversación en el sitio web, visita https://groups.google.com/d/msgid/fpga-wars-explorando-el-lado-libre/CAEQ-VCYEMPrO3PBVM7KeJgUu52Ohcm5ygGYiih8t1OBgK9gu3A%40mail.gmail.com.

Reply all

Reply to author

Forward

0 new messages