RISC-V and Posit

129 views

Skip to first unread message

Tommy Thorn

Mar 30, 2022, 2:20:48 PM3/30/22

to Unum Computing

Say I'm creating a RISC-V core, but want to base it on Posits. What is the *minimal* effort to get an as *useful of a result as possible*?

I'm sure this has been considered and debated already (and I apologize for missing it). I have seen John's RISC-V embedding, but I would consider a different approach:

# Strawman

Ignoring FP64 (double precision) for the moment, make all existing FP instructions use Posits. Some instruction become nops, others have no equivalents and becomes illegal instructions. With this approach, you'd essentially would only need to change the compilers/assemblers to emit posit constants instead of floats. You almost certainly will have to tweak libraries like libm and libc (the latter not much I suspect).

(Variation of the above: introducing dedicated Posit load/store instructions, making the original float load/store (flw/fsw) load/store IEEE-754 numbers and convert to/from Posit (and trap for NaN).)

For FP64 could might either expand it to Posit64 or simply map everything to Posit32.

# The Quine

This is an orthogonal issue and it's a bit of an awkward beast, but here's one option I'm considering that would allow most existing code to use the quine transparently:

This is an orthogonal issue and it's a bit of an awkward beast, but here's one option I'm considering that would allow most existing code to use the quine transparently:

- there are one [or more] quines

- at any point in time, a quine is either free or associated with an fp register

- a use of an fp register associated with a quine will convert the quine, update the fp register, and disassociate the quine (freeing it)

- a use of an fp register associated with a quine will convert the quine, update the fp register, and disassociate the quine (freeing it)

- an fma instruction, say fmadd.s rd,rs1,rs2,rs3 will allocate a free quine and associate it with rd.

- a special exception to the above: if rs3 is associated with quine, then ownership is transferred to rd.

Thus, an an example,

flw fs7, ...

fmadd fs7, fs1, fs2, fs7

fmadd fs7, fs3, fs4, fs7

fsw fs7, ....

will perform the two element dot-product using the quine without even having to know about it.

For context switching needs, there will be a way to save and restore the quine(s) via CSRs, TBD.

Admittedly there are rough edges here, but again, the focus was not on a perfect solution, but on a solution that would require minimal changes to compilers and libraries.

Thoughts, flames?

Tommy

Disclaimer: opinions are my own and doesn't in any way reflect anything about my employer

John Gustafson

Mar 30, 2022, 2:39:59 PM3/30/22

to Tommy Thorn, Unum Computing

Quick answer:

Don't re-invent the wheel. There are about a dozen RISC-V core implementations using posits, either open source or for commercial sale, like Calligo Tech and VividSparks. They've worked out the compiler and library issues. New ones are being created all the time.

As a follow-on to the Standard, we hope to write a "Guide for Conversion from Floats to Posits" that touch on all the things that can go wrong. It might be 20 pages long by the time we're done. Most of the hurdles can be automated, and I think we will see some very clever tools that, say, make sure all real inputs are specified in decimal (scientific) notation and not as hex or binary, and flag tests for NaN of the type "if (x != x) ..." that become "if (x == NaR)..." for posits. Codes that compute a machine epsilon and use that for convergence testing, say, will need a numerical analyst to straighten out.

The word is "quire", by the way, not "quine". When hardware designers complain that the quire takes too much space or energy, I tell them, "Then just provide it in software, using an integer vector." While we had a hardware register in mind originally, you can have any number of quire-format values in memory and the ratified Standard no longer treats the quire as a hardware register.

John

--

You received this message because you are subscribed to the Google Groups "Unum Computing" group.

To unsubscribe from this group and stop receiving emails from it, send an email to unum-computin...@googlegroups.com.

To view this discussion on the web visit https://groups.google.com/d/msgid/unum-computing/408a99c3-bff3-4550-944d-652522997d6cn%40googlegroups.com.

Art Scott

Apr 28, 2022, 8:27:55 PM4/28/22

to Unum Computing

Aloha all.

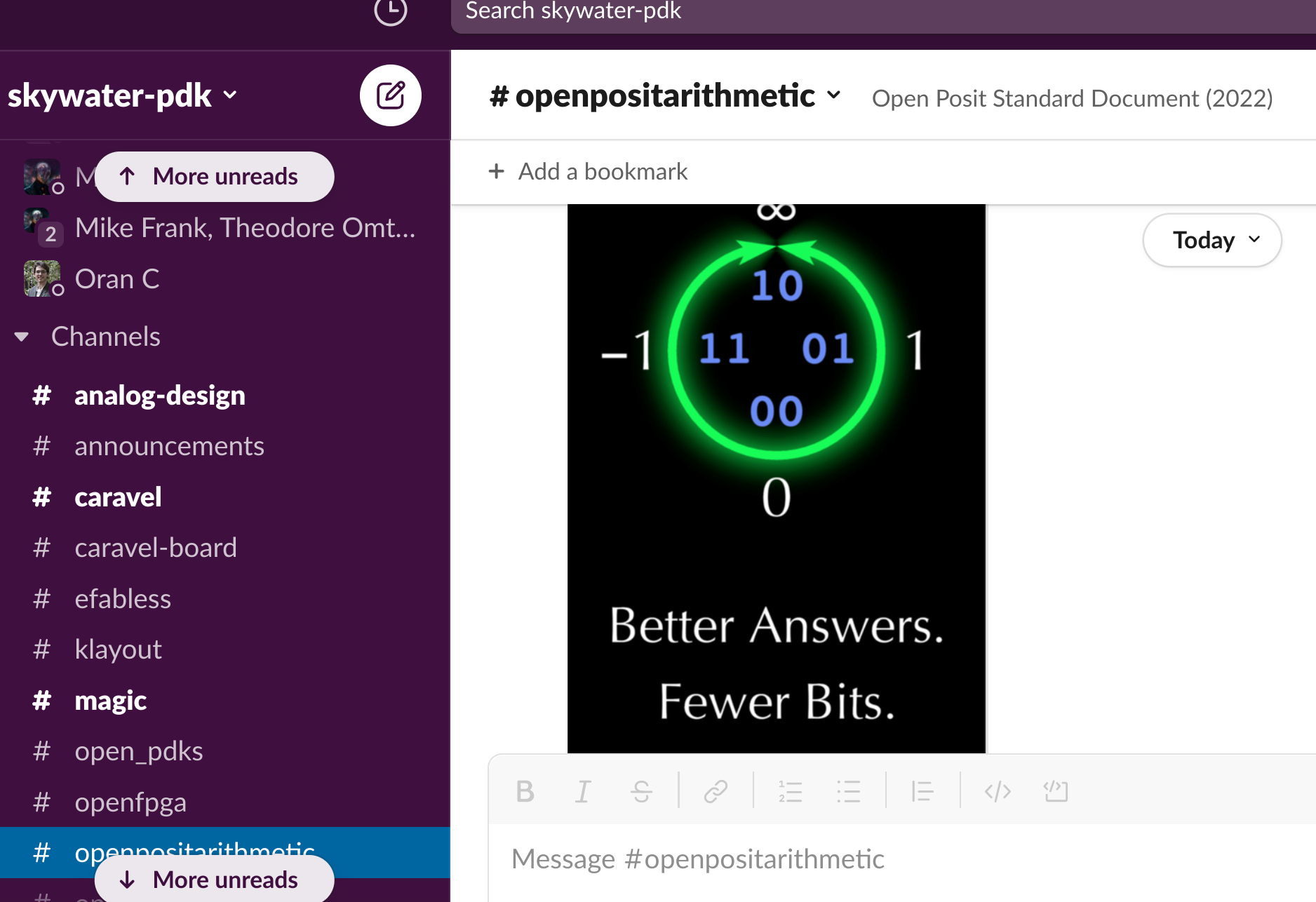

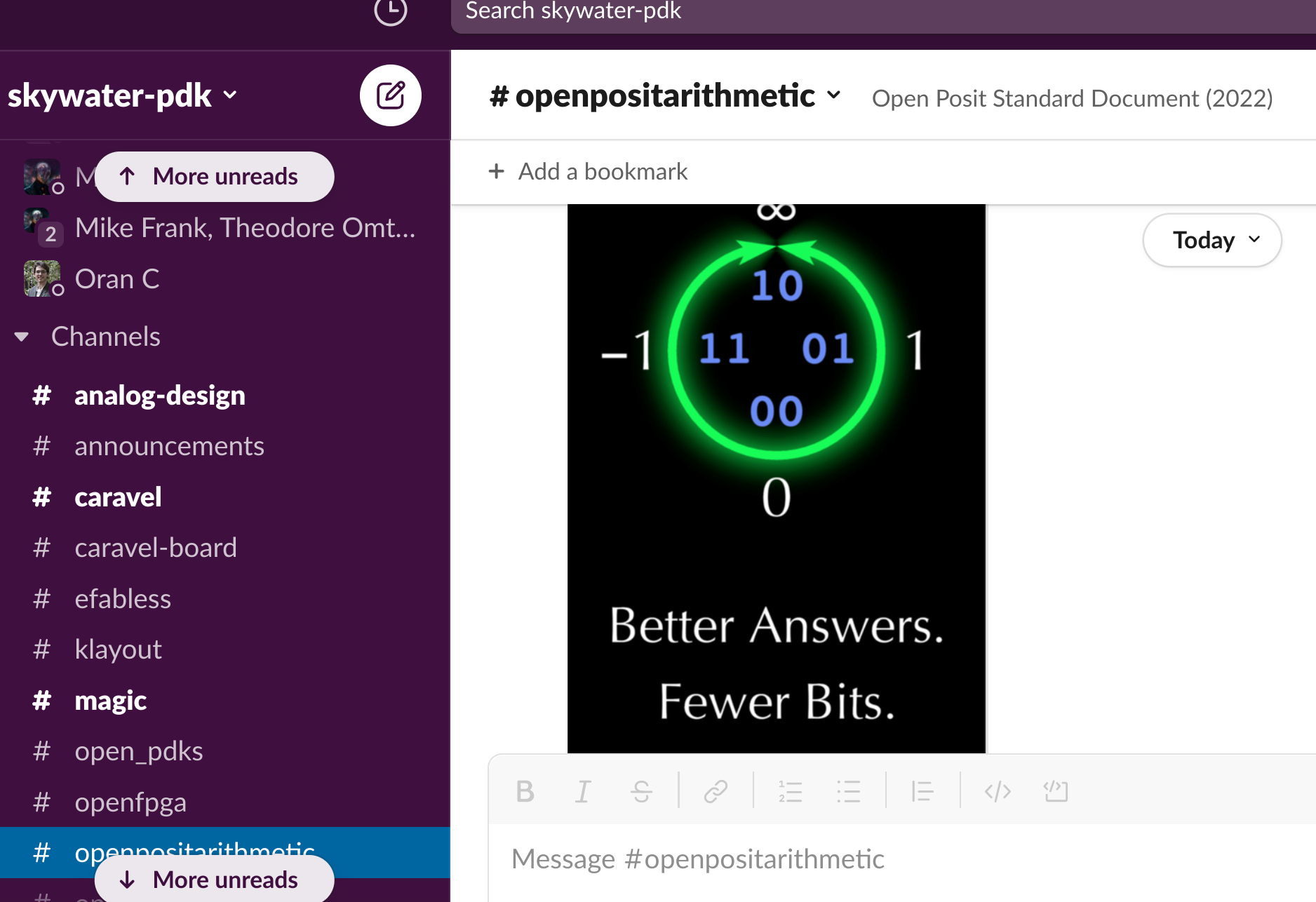

Make posit HW at free open Sky130 MPW ... got a posit co-processor idea?

RISC-V posit extension?

Make posit HW at free open Sky130 MPW ... got a posit co-processor idea?

RISC-V posit extension?

Now ... #openpositarithmetic channel for posit tm Next Generation Arithmetic @ Sky130 Slack

Reply all

Reply to author

Forward

0 new messages