Monday MPW-2 Update - Sep 26, 2022

Jeff

Hello everyone,

Please see updates for this week.

MPW-2 Silicon Testing

I/O Configuration

Automated testing has been completed across 18 parts.

Tests have been repeated across multiple test setups and run across operating voltages from 1.5 to 1.8V.

The optimal operating voltage for configuring IO ranges from part to part.

We continue to find 4 out of the 18 parts can be fully configured with all IO. Many of the others can configure 70-85% of the IO.

We have also brought up a second automated test setup and are working through debug to get it running in parallel.

Caravel Functionality

Extended function testing is running on parts with full IO configurations.

Tests include CPU stress, openRAM, DFFRAM, IRQ, UART, and other testing

Test results will be available in the next day or so

Automation

Temperature testing will be performed after the functional testing above completes.

MPW-2 Hardware

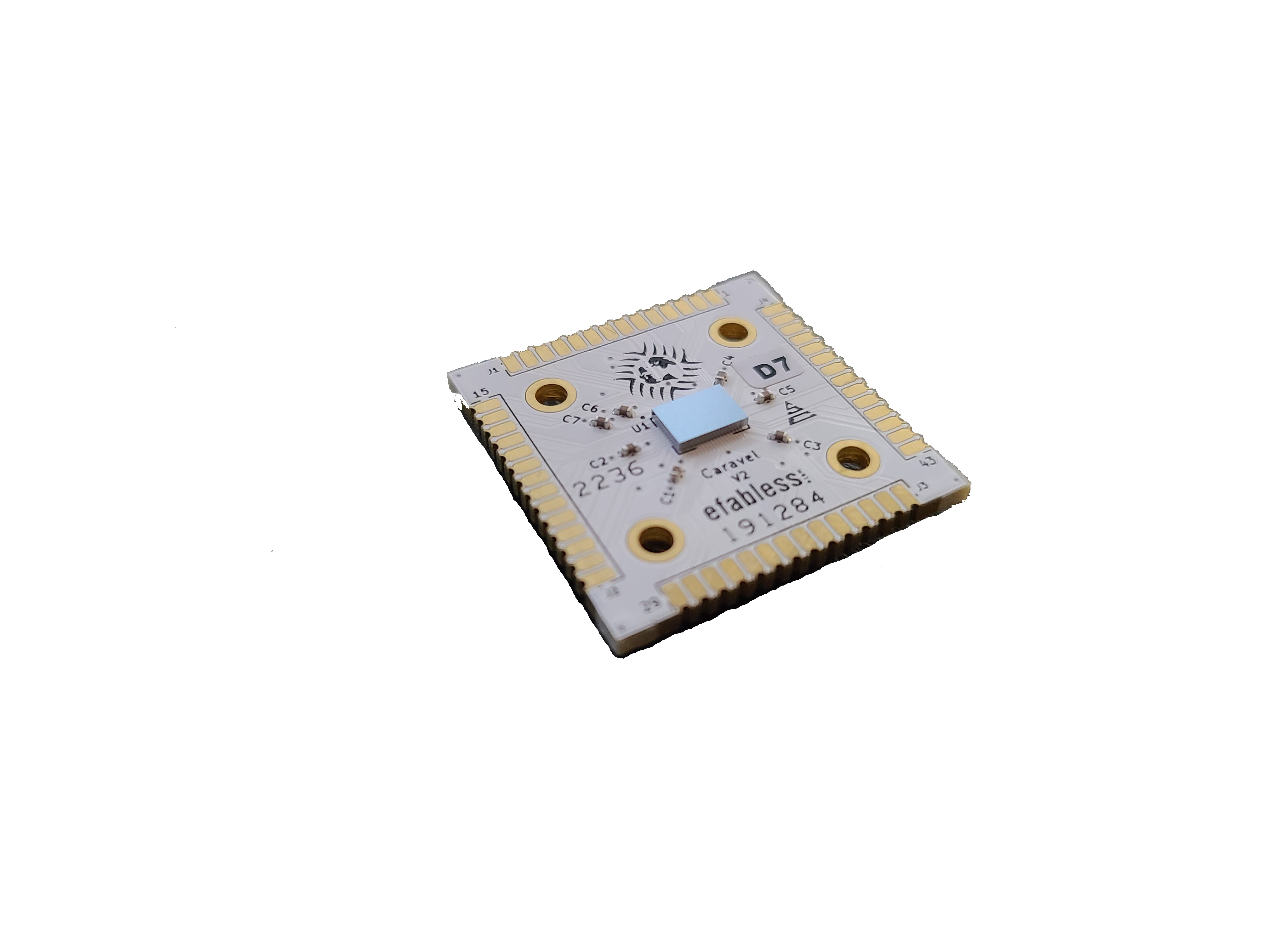

363 breakout board assemblies are back. The remaining assemblies are expected to arrive in the next day or two.

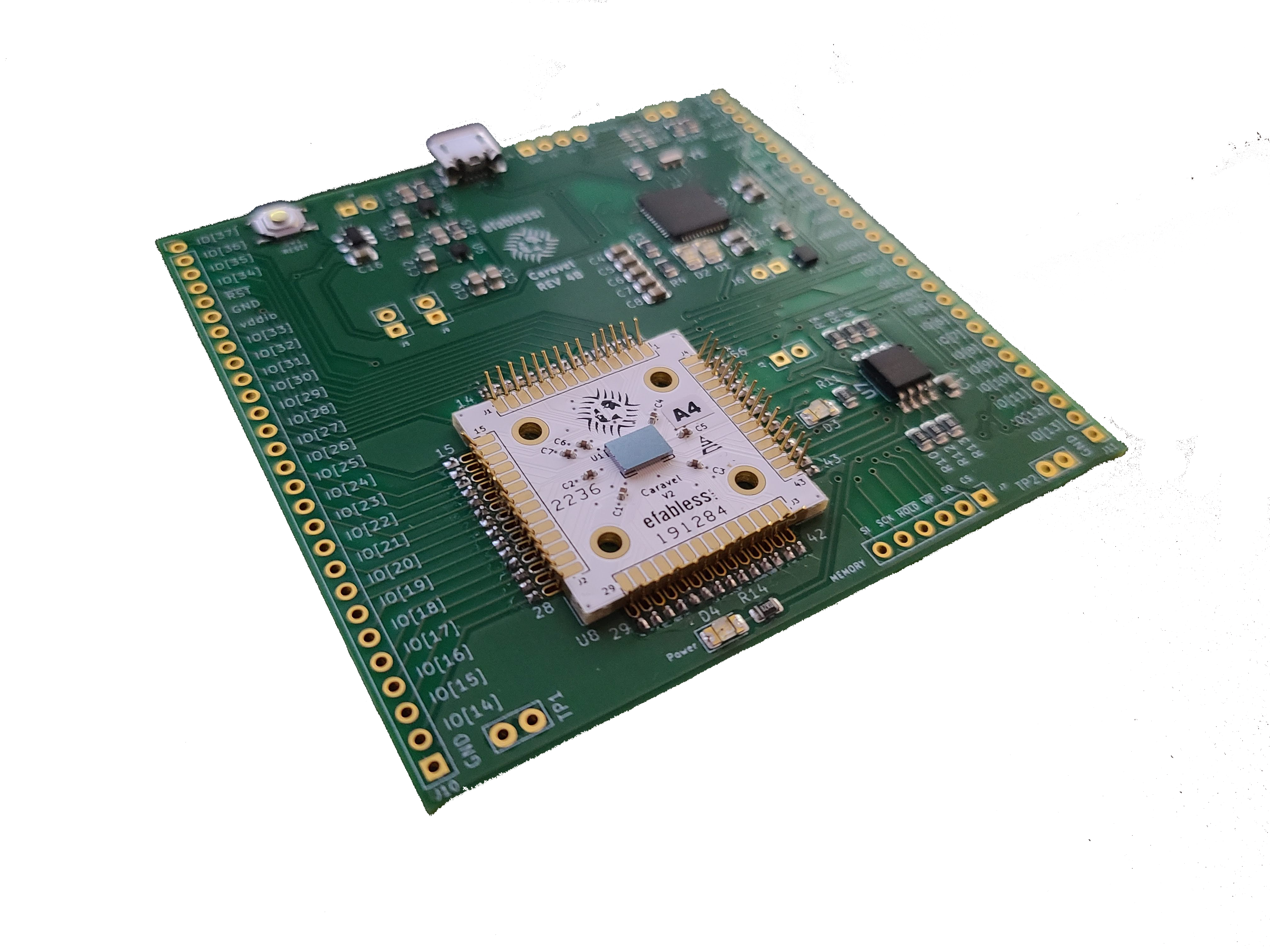

Samples for the main Caravel board have returned and passed an initial initial testing.

The following video shows installation of pins as well as flashing firmware and running a simple blink test.

Initial samples for a similar board in a Nucleo hat format are being fabricated for testing. Firmware for the configuration uses Micropython on the development board and initial testing has been completed on the Nucleo board talking to a Caravel.

The configuration will allow users to automate testing parts for their own projects to identify the part that will configure all IO required for their project and provide a configuration ‘string’ to be used by their firmware for setting up IO.

We are working to get the complete test configuration assemblies complete for shipping with the breakout boards to each project owner.

If anyone wishes to receive their parts ahead of getting the main board plus Nucleo setup, please reach out to me on Slack at @jeffdi or via email at open...@efabless.com

MPW-2 Simulation

We now have STA and simulation results that are consistent with failures seen in Silicon testing.

This now allows for implementing changes to correct the timing issues and confirm through analysis and simulation that they have been resolved.