eADR characteristics at failure

307 views

Skip to first unread message

George Hodgkins

Oct 20, 2021, 12:50:23 PM10/20/21

to pmem

Hi all,

My research group is working on a project which leverages eADR, and we've run into a couple of questions about how it behaves at power failure.

1. An external power source is required; how much energy does this source have to supply for a successful drain? How is the power supplied (i.e. through existing supply lines, dedicated power supply connector, direct connection from outside the box) and to what component(s) is it supplied (i.e. processor, memory controller, individual DIMMs)?

2. How is the drain operation activated at failure (i.e. ACPI event, dedicated detection circuit, etc)? Does it occur concurrently with the hold-up period of the main supply, or afterwards?

Thanks in advance for your help.

-George

Andy Rudoff

Oct 20, 2021, 2:24:43 PM10/20/21

to pmem

Hi George,

eADR is a platform-level feature, so there are multiple answers to your question depending on how the platform vendor implements it. Here's a "general" answer, but details may differ. The stored energy required for eADR is typically provided by a battery. There's a specification that Intel provides platform vendors that describes the amount of energy required to flush persistent data from the CPU caches to persistent media. For eADR the power is used to keep the CPUs up in order to execute BIOS code that flushes the CPU caches, and then as the final step in the eADR flow, an ADR flow is triggered which ensures persistent data still in the memory controller queues is flushed to the persistent media. Extra signals, motherboard traces, and power supply requirements were added for ADR (years ago now), and eADR adds the requirement that the system can run the BIOS flow I just described. So I would expect such a system to have a more complex power subsystem with the battery integrated, but I can't think of additional changes beyond that.

As for how it is triggered, the power supply detects the loss of power and asserts a signal that is routed to the CPLD, which in turn signals the PCH to trigger eADR. this triggers an SMI which causes SMM code in the BIOS to run as I described above.

Steve Scargall

Oct 20, 2021, 4:02:51 PM10/20/21

to pmem

Hi George,

The only OEM server that I am aware of that implements eADR to the specification is the HPe Superdome Flex. Superdome Flex 280 server management hardware built into the

solution monitors AC input power all the way through downstream low voltage

converters/regulators in order to generate a true “powerfail” signal that initiates the cache flushing process described by Andy. This mechanism, is independent to external AC power conditioning

or UPS gear that might or might not be added within the rack.

/Steve

Wentao Huang

Nov 3, 2021, 1:07:31 AM11/3/21

to pmem

Hi Steve,

Are there any other servers that implement eADR?

I just check with the customer service of HPe, they told me that Superdome Flex 280 not yet implemented eADR. Not sure if it is true (customer service may be not familiar with eADR concept).

Best,

Wentao

Steve Scargall

Nov 3, 2021, 5:43:45 AM11/3/21

to pmem

I do not know of any OEM platforms, other than the HPe Superdome. Most OEMs do have a BIOS option to enable it for testing (non-Production) environments.

Anton Gavriliuk

Nov 3, 2021, 6:19:59 AM11/3/21

to Steve Scargall, pmem

>

I just check with the customer service of HPe

Regarding eADR on HPE servers -

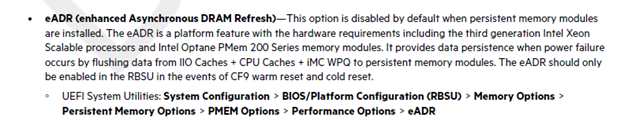

eADR is enabled within the RBSU. Please see below.

Any Gen10 Plus ICX servers that support Barlow Pass can enable eADR and these servers are

- DL360 Gen10 Plus

- DL380 Gen10 Plus

- SY480 Gen10 Plus

- Apollo 4200 Gen10 Plus

- Apollo 2000 Gen10 Plus

Anton

ср, 3 нояб. 2021 г. в 11:43, Steve Scargall <steve.s...@intel.com>:

--

You received this message because you are subscribed to the Google Groups "pmem" group.

To unsubscribe from this group and stop receiving emails from it, send an email to pmem+uns...@googlegroups.com.

To view this discussion on the web visit https://groups.google.com/d/msgid/pmem/bd124932-68b2-43f0-b79e-1803ed754a69n%40googlegroups.com.

Wentao Huang

Nov 3, 2021, 6:35:50 AM11/3/21

to pmem

Thanks, Anton,

Would you mind sharing the link? Thanks.

Best,

Wentao

Reply all

Reply to author

Forward

0 new messages