Interrupts in OpenPiton+Ariane

34 views

Skip to first unread message

Abdullah Yıldız

Apr 11, 2021, 6:22:15 AM4/11/21

to OpenPiton Discussion

Hi,

According to OpenPiton FPGA Prototype Manual (fpga_man):

Interrupts are generated by the Ethernet Lite IP core upon a successful transmit or receive. The signal is synchronized to the clock domain of ciop_iob, which is responsible for sending the actual interrupt packet to the core.

I wonder why the net/uart interrupt signal is sent to the core both through ciop_iob and plic instead of just plic.

I also wonder why PITON_UART_INTR macro is not defined in ciop_iob to enable sending the packet that is related to interrupt to the core.

"Bu mesaj (ve ekleri) gizli bilgi içermektedir ve sadece gönderilen kişiye yöneliktir. Bu e-mailin muhatabı değilseniz veya içeriği ile ilginiz yoksa, Yeditepe Üniversitesinin onayı olmaksızın bu mesajın okunması, değiştirilmesi, kopyalanması, üçüncü kişilere açıklanması, yayınlanması, ifşa edilmesi veya iletilmesi yasaktır. Bu mesajın gönderilmek istendiği kişi değilseniz (ya da bu e-posta'yı yanlışlıkla aldıysanız), lütfen yollayan kişiyi hemen haberdar ediniz ve mesajı sisteminizden derhal siliniz. E-mail iletiminin güvenli veya hatasız olduğunun garantisi olmadığından geç veya eksik iletim veya içerik ve bilgilerde eksiklik, kayıp, değişiklik veya virüs olabilir. Bu nedenle, bu mesajın iletiminden dolayı, Yeditepe Üniversitesi , içerikteki hata, eksiklik, doğruluğun ve gizliliğin ihlalinden veya bu yolla bilgi paylaşımı, iletimi, depolanması gibi herhangi bir kullanımından hiçbir şekilde sorumlu değildir. Bu mesajın içeriği yazarına ait olup, Üniversitemizin görüşlerini içermeyebilir.

Bu mesajın içeriğinde geçen Üniversitemizin ad veya nanıma yaratılan fikri ve sınai haklar Üniversitemize ait olup, maddi ve manevi tüm hakları saklıdır.”

“This Message (including any attachments) contains confidential information and is intended only for the individual named. If you are not the named adressee or not related with the content of this Message, you are forbidden to read, disseminate, distribute, copy, reproduce or modify this mail by Yeditepe University. Please notfy the sender immediately if you have received this e-mail by mistake and delete this e-mail from your system. E-mail transmisson can not be guaranteed to be secure or error-free as the mail may arrive late or incomplete or the information could be intercepted, corrupted, lost, destroyed, amended, , or contain viruses. Yeditepe University therefore does not accept liability for any errors, loss of integrity or confidentiality or ommissions in the contents of this Message or for the information transmission, reception, storage of use of such in any way whatsoever, which arise as a result of e-mail transmission. Any opinions expressed in this message are those of the author and may not necessarily reflect the opinions of Our University.

Copyright in documents created by or on behalf of our University remains vested in us, and we assert all of our moral and intellectual property rights."

Jonathan Balkind

Apr 12, 2021, 2:42:42 PM4/12/21

to OpenPiton Discussion

Hi Abdullah,

You're reading about the SPARC-specific interrupt infrastructure. The doc just hasn't been fully updated for RISC-V. For Ariane it uses the standard RISC-V PLIC and CLINT mechanisms. You can see how those are wired in chipset_impl. There might be wiring from the devices into ciop_iob but the module itself isn't being used for RISC-V.

Thanks,

Jon

--

You received this message because you are subscribed to the Google Groups "OpenPiton Discussion" group.

To unsubscribe from this group and stop receiving emails from it, send an email to openpiton+...@googlegroups.com.

To view this discussion on the web, visit https://groups.google.com/d/msgid/openpiton/CABvne69CYovKSgsCGX3Hf2ETMNNVUu-VxSDPbn1NZX2JYjQXBQ%40mail.gmail.com.

Abdullah Yıldız

Apr 13, 2021, 2:45:52 AM4/13/21

to Jonathan Balkind, OpenPiton Discussion

Hi Jonathan,

Thanks for your support.

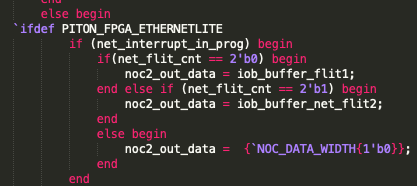

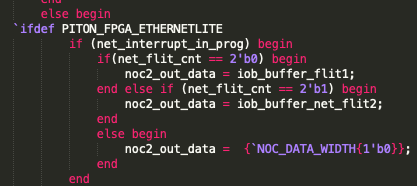

As you stated, the ciop_iob module is used in the default FPGA prototype to drive iob_packet_filter. I wanted to ask this since I am not very familiar with the OpenPiton NOC interface:

To view this discussion on the web, visit https://groups.google.com/d/msgid/openpiton/CAJm4tWaj383ahNYfVe42nXft8wxxT0%2BuvZqLJNf33RVhsDzoBg%40mail.gmail.com.

Jonathan Balkind

Apr 13, 2021, 2:53:47 AM4/13/21

to OpenPiton Discussion

Yeah, you can safely ignore ciop_iob for the purposes of Ariane in OpenPiton's FPGA environment.

Jon

To view this discussion on the web, visit https://groups.google.com/d/msgid/openpiton/CABvne68BWTBB22Rhbg5EGzMLNeNp93FGjRpbfyOQV2e8VCbb9A%40mail.gmail.com.

Abdullah Yıldız

Apr 13, 2021, 3:10:00 AM4/13/21

to Jonathan Balkind, OpenPiton Discussion

OK. Thanks.

To view this discussion on the web, visit https://groups.google.com/d/msgid/openpiton/CAJm4tWZYQd%3DBEU7VCwYdmSjZhoELRaZ3uAvzHHRi5SQ%2B%3De8Gtw%40mail.gmail.com.

Reply all

Reply to author

Forward

0 new messages