Unlikely "sighting" of an 1130

Bob Flanders

Paul Anagnostopoulos

Bob Flanders

Thank you. Very cool.

Bob

> You received this message because you are subscribed to the Google Groups "IBM1130" group.

> To unsubscribe from this group and stop receiving emails from it, send an email to ibm1130+u...@googlegroups.com.

> To view this discussion on the web visit https://groups.google.com/d/msgid/ibm1130/4a2205e1-e82c-4409-a102-7b0f00fa652c%40googlegroups.com.

> For more options, visit https://groups.google.com/d/optout.

Eddy Quicksall

Eddy

---

This email has been checked for viruses by Avast antivirus software.

https://www.avast.com/antivirus

Paul Anagnostopoulos

richard...@comcast.net

Instruction timing is given in the Functional Characteristics Manual. There are two tables, one for 3.6 us core and one for 2.2 us. The fastest instructions took 2 cycles. A LOAD instruction would vary between 4.6 and 6.8 us depending on the tag bits, the difference being one more memory cycle for indirect or indexed. An ADD instruction is ugly and in the short form would vary between 4.9 and 7.9 us while the long form would vary between 7.1 and 10.1 us. Why the variation? Well, the 1130 CPU adder didn’t deal with carry-in to each bit position. Instead it registered the carries and repeatedly added until the carries were gone. So, a variable number of clocks per ADD.

The worst case is DIVIDE where the short form varies between 46.4 and 92.1 us while the long form varies between 48.6 and 94.4 us.

Assigning a MIPS to this processor is going to be difficult. It’s going to depend on the instruction mix and the number of carries during ADD/SUB.

So, call it 6 us per instruction or 0.167 MIPS but if somebody said it was half that, I wouldn’t argue. And that’s for the 2.2 us core. It’s about 0.111 MIPS for the 3.6 us core. Or half that…

From: ibm...@googlegroups.com <ibm...@googlegroups.com> On Behalf Of Paul Anagnostopoulos

Sent: Thursday, June 27, 2019 7:21 AM

To: IBM1130 <ibm...@googlegroups.com>

Subject: Re: [IBM1130] Re: Unlikely "sighting" of an 1130

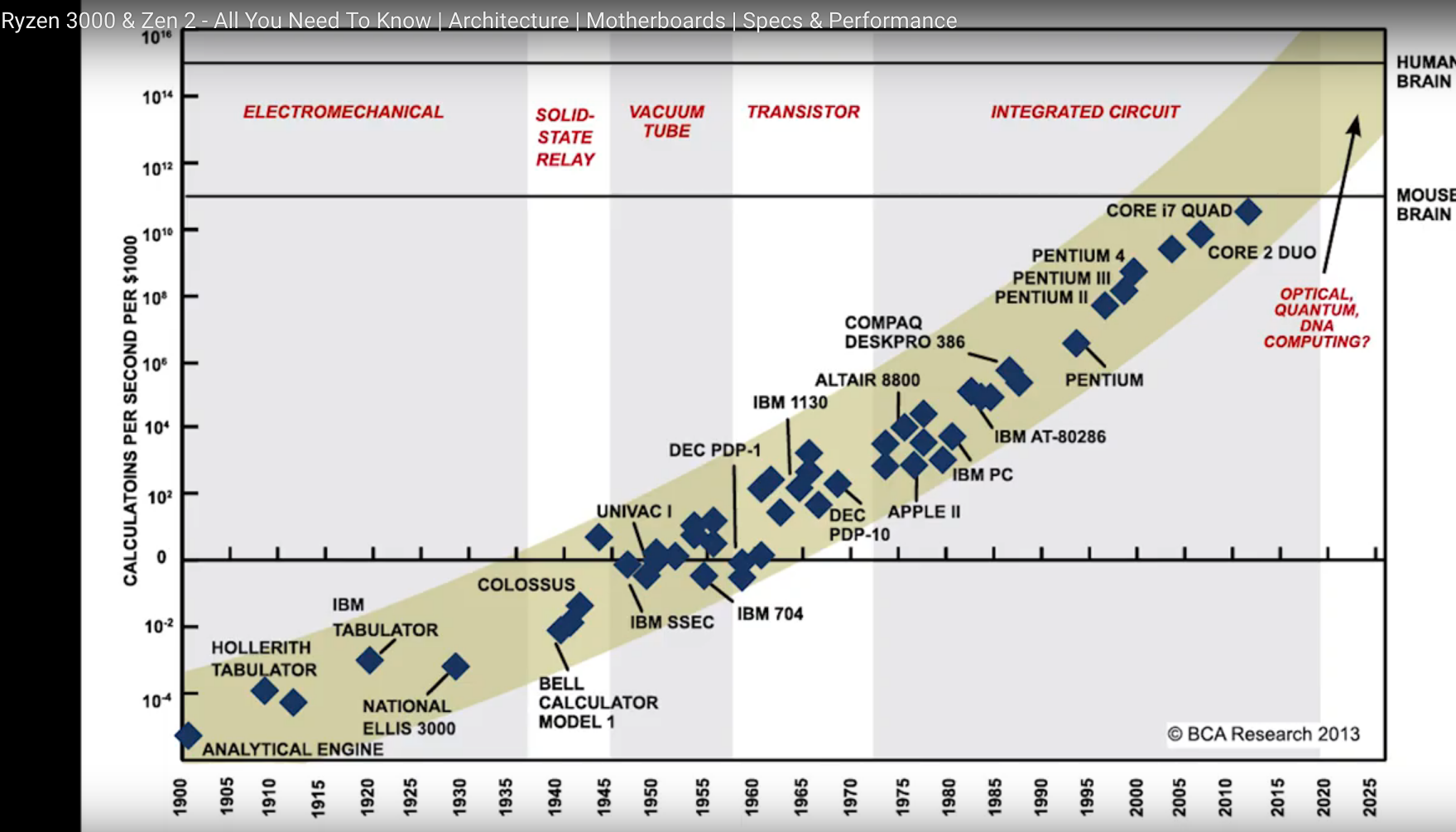

Now that I look at that table more carefully, the MIPS value for the 1130 is clearly wrong. A MIPS rating of .0000302 would be about 30 instructions per second. I wonder how he normalized the ratings? The IBM S/360 model 65 looks about right, as does the canonical VAX-11/780.

So, can we calculate a reasonable MIPS rating for a 2.2 us 1130? What was the average number of cycles per instruction? Around 2?

~~ Paul

--

You received this message because you are subscribed to the Google Groups "IBM1130" group.

To unsubscribe from this group and stop receiving emails from it, send an email to ibm1130+u...@googlegroups.com.

To view this discussion on the web visit https://groups.google.com/d/msgid/ibm1130/a6c52e60-3fe2-460d-b4ab-dea6f849e7d5%40googlegroups.com.

Paul Anagnostopoulos

On Thursday, June 27, 2019 at 3:44:52 PM UTC-4, Richard Stofer wrote:

Instruction timing is given in the Functional Characteristics Manual. There are two tables, one for 3.6 us core and one for 2.2 us. The fastest instructions took 2 cycles. A LOAD instruction would vary between 4.6 and 6.8 us depending on the tag bits, the difference being one more memory cycle for indirect or indexed. An ADD instruction is ugly and in the short form would vary between 4.9 and 7.9 us while the long form would vary between 7.1 and 10.1 us. Why the variation? Well, the 1130 CPU adder didn’t deal with carry-in to each bit position. Instead it registered the carries and repeatedly added until the carries were gone. So, a variable number of clocks per ADD.

The worst case is DIVIDE where the short form varies between 46.4 and 92.1 us while the long form varies between 48.6 and 94.4 us.

Assigning a MIPS to this processor is going to be difficult. It’s going to depend on the instruction mix and the number of carries during ADD/SUB.

So, call it 6 us per instruction or 0.167 MIPS but if somebody said it was half that, I wouldn’t argue. And that’s for the 2.2 us core. It’s about 0.111 MIPS for the 3.6 us core. Or half that…

Eddy Quicksall

This makes me think of the Meta-4 which emulated the 1130. As was explained to me on the Meta-4 they didn’t use a clock, they used timing loops and timed them so all the signals arrived at the gate at the same time. The Meta-4 was a good bit faster than the 1130.

Eddy

From: ibm...@googlegroups.com [mailto:ibm...@googlegroups.com] On Behalf Of Paul Anagnostopoulos

Sent: Friday, June 28, 2019 7:24 AM

To: IBM1130

Subject: Re: [IBM1130] Re: Unlikely "sighting" of an 1130

--

You received this message because you are subscribed to the Google Groups "IBM1130" group.

To unsubscribe from this group and stop receiving emails from it, send an email to ibm1130+u...@googlegroups.com.

To view this discussion on the web visit https://groups.google.com/d/msgid/ibm1130/247f9db7-21ac-4135-8458-e85334df6929%40googlegroups.com.

For more options, visit https://groups.google.com/d/optout.

Paul Anagnostopoulos

On Friday, June 28, 2019 at 8:55:56 AM UTC-4, Eddy Quicksall wrote:

This makes me think of the Meta-4 which emulated the 1130. As was explained to me on the Meta-4 they didn’t use a clock, they used timing loops and timed them so all the signals arrived at the gate at the same time. The Meta-4 was a good bit faster than the 1130.

richard...@comcast.net

There’s a certain symmetry in using an 1130 to debug the microcode of the Meta 4 emulating an 1130.

Path delay is a lot shorter with modern CPUs but it’s still a speed limiter. I remember where the CDC 6400 had clock signal delays timed by wire length to guarantee setup times as signals moved from bay to bay. It was a really big deal! But it definitely used clocks.

An asynchronous design must be really difficult.

In my FPGA projects, the timing report shows that path delay often exceeds logic delay.

From: ibm...@googlegroups.com <ibm...@googlegroups.com> On Behalf Of Paul Anagnostopoulos

Sent: Saturday, June 29, 2019 4:11 AM

To: IBM1130 <ibm...@googlegroups.com>

Subject: Re: [IBM1130] Re: Unlikely "sighting" of an 1130

--

You received this message because you are subscribed to the Google Groups "IBM1130" group.

To unsubscribe from this group and stop receiving emails from it, send an email to ibm1130+u...@googlegroups.com.

To view this discussion on the web visit https://groups.google.com/d/msgid/ibm1130/b036bce4-cc95-4973-bf6a-c2e454b48357%40googlegroups.com.

Eddy Quicksall

A friend of mine wrote an upgrade of DSC’s 1130 emulation. To debug it he wrote an emulation of the Meta-4 machine on the 1130 to run his emulator which itself ran as an IBM 1130 running DM2. It ran so slow that it took a few seconds for the typewrite to echo they character as you typed. I have a customer that still runs his data processing business using my GA1830 emulation (a cross between the 1800 and 1130). I have not tested lately but when I wrote it around 1990 it ran a hundred or so faster than the 1130. I wonder how fast it is now.

Eddy

To view this discussion on the web visit https://groups.google.com/d/msgid/ibm1130/001b01d52e8d%243ea45080%24bbecf180%24%40comcast.net.

For more options, visit https://groups.google.com/d/optout.

Eddy Quicksall

That’s cool. I still have one up in the attic along with a memory board. Did Brown ever get DNA’s TSO system (a timesharing system for the IBM 1130/Meta-4/GA1830/CHI2130))? That is what my customer is running.

Eddy

From: ibm...@googlegroups.com [mailto:ibm...@googlegroups.com] On Behalf Of Paul Anagnostopoulos

Sent: Saturday, June 29, 2019 7:11 AM

To: IBM1130

Subject: Re: [IBM1130] Re: Unlikely "sighting" of an 1130

--

You received this message because you are subscribed to the Google Groups "IBM1130" group.

To unsubscribe from this group and stop receiving emails from it, send an email to ibm1130+u...@googlegroups.com.

To view this discussion on the web visit https://groups.google.com/d/msgid/ibm1130/b036bce4-cc95-4973-bf6a-c2e454b48357%40googlegroups.com.

For more options, visit https://groups.google.com/d/optout.