please help with a verilog programm

Pablo Meraz

Dear Friends:

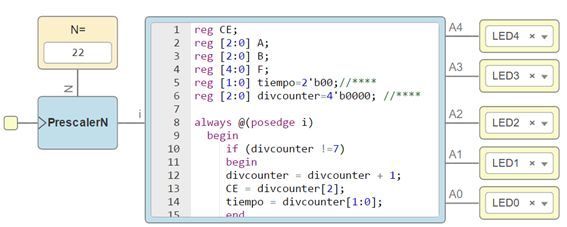

I have read something about verilog and I really like electronics, but I have no experience with Verilog. I have an ICE40- HX8K - Breakout Board card.I have been working on a large project and it is not working for me. When doing various tests, I found a strange error in an always block. I removed several lines of code to make it as simple as possible but where the error can still be detected

The module runs activated by a clock with a prescaler of N = 22 to produce a very low frequency, this clock activates a counter from 0 to 7, when it reaches the value of 7, by code it is no longer increased. When the counter goes through binary 101, register C3 is activated and when the counter reaches 111, register C4 is activated.Additionally CY = C3 | C4, which must be activated whether C3 or C4 is activated

The program is as follows:

01 reg CE;

02 reg [2:0] A;

03 reg [2:0] B;

04 reg [4:0] F;

05 reg [1:0] tiempo=2'b00;//****

06 reg [2:0] divcounter=4'b0000; //****

07

08 always @(posedge i)

09 begin

10 if (divcounter !=7)

11 begin

12 divcounter = divcounter + 1;

13 CE = divcounter[2];

14 tiempo = divcounter[1:0];

15 end

16 end

17

18 reg C3=1'b0; //**

19 reg C4=1'b0; //**

20 reg CY;

21

22 always @(*) begin

23 C3= (CE==1) & (tiempo==2'b01);

24 C4= (CE==1) & (tiempo==2'b11);

25 CY=C3 | C4;

26 end

27

28 always @(posedge CY) begin

29 F[4]=CY;

30 F[3]=C3;

31 F[2]=C4;

32 F[1]=0;

33 F[0]=1;

34 end

35

36 assign A4=F[4];

37 assign A3=F[3];

38 assign A2=F[2];

39 assign A1=F[1];

40 assign A0=F[0];

Alexandre Dumont

Jorge Garcia Mateos

Hi Pablo, the Alexandre's advice to use a testbench is great and will give you more control and capability to check your code by yourself. You have to install "gtkwave", if you use icestudio you have "iverilog" installed. I've rewritten your code as:

and made a testbench "test_tb.v" for it:

--

Has recibido este mensaje porque estás suscrito al grupo "FPGAwars: explorando el lado libre" de Grupos de Google.

Para cancelar la suscripción a este grupo y dejar de recibir sus mensajes, envía un correo electrónico a fpga-wars-explorando-el...@googlegroups.com.

Para ver esta conversación en el sitio web, visita https://groups.google.com/d/msgid/fpga-wars-explorando-el-lado-libre/ec7d2ba1-6bab-40c4-b349-ccac992996fen%40googlegroups.com.

Alexandre Dumont

Alexandre Dumont

Alexandre Dumont

Eduardo Rodríguez

Summary in spanish... https://www.linuxito.com/programacion/1338-asignaciones-bloqueantes-y-no-bloqueantes-en-verilog

Jorge García Mateos

Alexandre Dumont

--

Has recibido este mensaje porque estás suscrito a un tema del grupo "FPGAwars: explorando el lado libre" de Grupos de Google.

Para cancelar la suscripción a este tema, visita https://groups.google.com/d/topic/fpga-wars-explorando-el-lado-libre/XNxr1KauHv0/unsubscribe.

Para cancelar la suscripción a este grupo y a todos sus temas, envía un correo electrónico a fpga-wars-explorando-el...@googlegroups.com.

Para ver esta conversación en el sitio web, visita https://groups.google.com/d/msgid/fpga-wars-explorando-el-lado-libre/34c15ef0-cddd-4f06-9218-c47eb7673e02n%40googlegroups.com.

Jorge Garcia Mateos

It has sense. Thanks!

Has recibido este mensaje porque estás suscrito al grupo "FPGAwars: explorando el lado libre" de Grupos de Google.

Para cancelar la suscripción a este grupo y dejar de recibir sus mensajes, envía un correo electrónico a fpga-wars-explorando-el...@googlegroups.com.

Para ver esta conversación en el sitio web, visita https://groups.google.com/d/msgid/fpga-wars-explorando-el-lado-libre/CALTA55H3i%3Dxvskm%2B6SPM2afQHDCj0OGNaPWVz4Uvis6%2BXBbyag%40mail.gmail.com.