Ayuda pinout pantalla banghó

900 views

Skip to first unread message

Carlos Pantelides

Jun 18, 2022, 3:56:39 PM6/18/22

to Embebidos32

Hola

Antes que nada, con lo que voy a preguntar me siento como cuando viene alguien de perfil puramente comercial cero técnico y dice cosas como "programar en html", por favor sepan disculpar mi baches de conocimiento.

Pregunta corta:

¿Sería factible hacer funcionar una pantalla HannStar HSD100IFW1-A00 rescatada de una bangho b-n0x1 desde una edu-ciaa-fpga o algún microcontrolador?

Mirando la datasheet:

- veo que dice "One channel LVDS interface"

- entiendo que eso usa "pares diferenciales"

- me recontra suena por haber oído en uno de los videos que no están expuestos

- y además, la datasheet de lattice (ice40) dice ser LVDS25 que me imagino no es compatible con

Datos extras:

Obviamente, no existe tal datasheet.

Quizás lo que me hace falta es leer un cierto artículo para orientarme, pero no sabría cuál.

Leyendo atentamente la datasheet, veo que dice que tiene "One channel LVDS interface"

Gracias y saludos

Pablo A. Llanos

Jun 18, 2022, 8:32:30 PM6/18/22

to embeb...@googlegroups.com

Hola Carlos,

Buenísima analogía pero sin duda no es tu caso! Vamos con algunas respuestas:

Mirando la datasheet:

- veo que dice "One channel LVDS interface"

- entiendo que eso usa "pares diferenciales"

Sí, en efecto, son 4 pares diferenciales de los cuáles 3 se utilizan para transmitir las señales de los pixels y un par diferencial para el clock. En el caso de este LCD utiliza una trama RGB666 (6 bits para cada color).

- y además, la datasheet de lattice (ice40) dice ser LVDS25 que me imagino no es compatible con

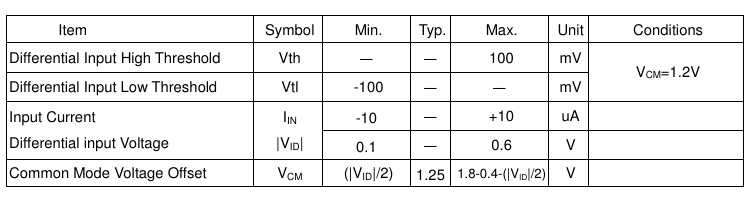

Bien, lo que tienes que tener en cuenta es que los valores máximos y mínimos que genera el FPGA no superen los valores del controlador del TFT. El Hannstar trabaja con una señal diferencial mínima de 100mV, máxima de 600mV con un offset típico de 1.2V, si compartes el datasheet del FPGA te puedo ayudar a chequear esto.

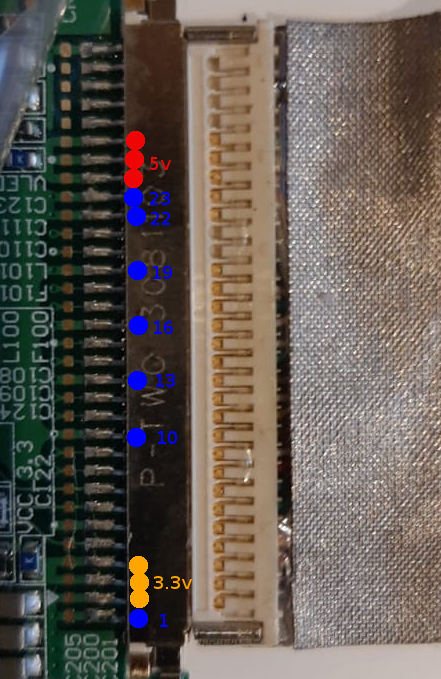

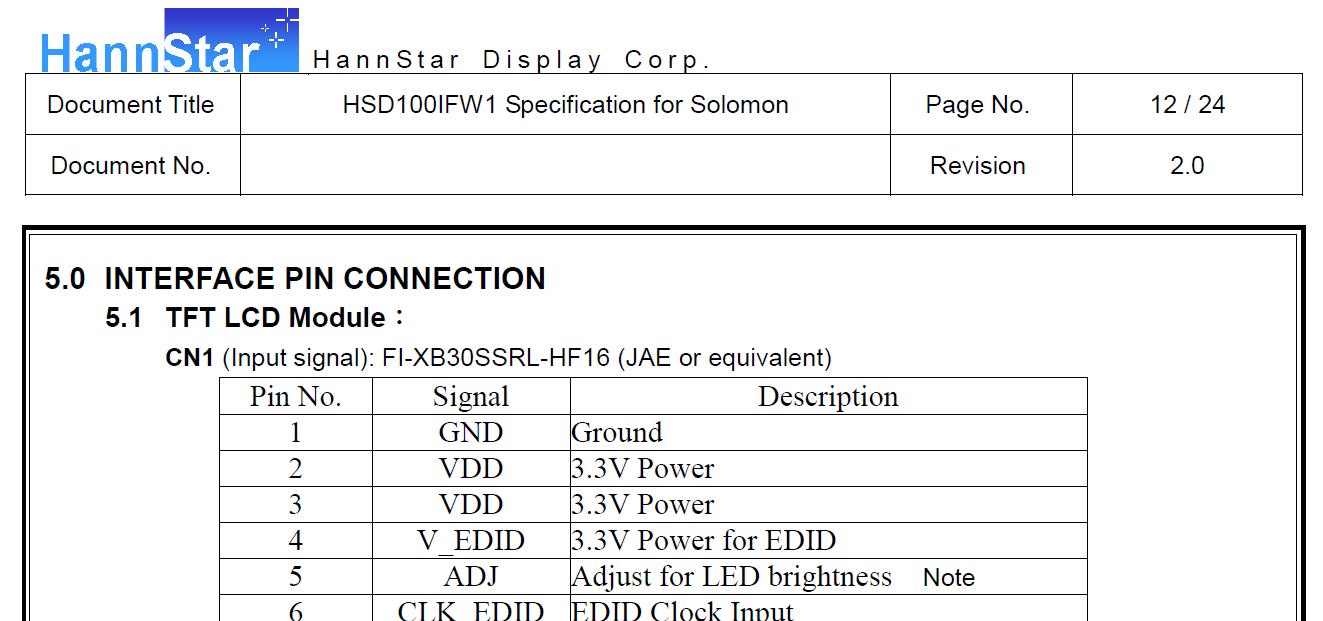

Según la datasheet de HannStar HSD100IFW1-A00 tiene 30 pines en el conector, pero, la vida nunca es fácil y la pantalla en sí tiene 32 pines

En realidad son 30 pines de señales, lo que ves como primer y último pin son conexiones a masa o al chasis del connector:

Ten en cuenta también los requerimientos de memoria que vas a necesitar para generar las imágenes del TFT. Lo ideal es que utilices double buffering (trabajas en un framebuffer y muestras otro), ese display tiene 1024 x 600 pixels y 262144 colores, vas a necesitar para cada framebuffer 3 * 1024 * 600 = 1843200 bytes (aproximadamente 1.76 MB de RAM), usando double buffering serían 3.515 MB.

Abajo está mi mail y teléfono, si te puedo ayudar en algo, no dudes en escribirme.

Saludos cordiales,

Pablo Llanos Clariá

Embedded Linux Expert

UNITED CODERS

--

-- Recibiste este mensaje porque estás suscripto al Grupo Google Embebidos32. Para postear en este grupo, escribe un email a embeb...@googlegroups.com. Para des-suscribirte, envía un email a embebidos32...@googlegroups.com. Para más opciones, visita el sitio del grupo en https://groups.google.com/d/forum/embebidos32?hl=es

---

Has recibido este mensaje porque estás suscrito al grupo "Embebidos32" de Grupos de Google.

Para cancelar la suscripción a este grupo y dejar de recibir sus mensajes, envía un correo electrónico a embebidos32...@googlegroups.com.

Para ver esta conversación en el sitio web, visita https://groups.google.com/d/msgid/embebidos32/CA%2BPxht0BG1%3DaqmJPjFFzOjDsehDfLF9MUpEW3xdzkik5QwH6%2Bg%40mail.gmail.com.

Carlos Pantelides

Jun 19, 2022, 9:58:16 PM6/19/22

to Embebidos32

Muchas gracias por la dedicación, continúo algunos puntos que ya sé, el resto uno de estos días a medida que asimile lo que mandaste...

"los requerimientos de memoria", sería muy baja, utilizando técnicas arcaicas (https://8bitworkshop.com/v3.9.0/?file=digits10.v&platform=verilog) caracteres monocromáticos, puede ser desde tan poco como (40 x 25 = 1k), (80 x 25 = 2k) o incluso que haga volcado de la RAM del programa [1], recuerdo hace muchas décadas en la escuela usar unas computadoras IBM en el lab que había en Pueyrredon e Independencia creo, algo del CONET, tenía un switch que alternaba entre la terminal común y eso, era fascinante aunque completamente incompresible, como 15 años antes de Matrix, tenían disketes de 8".

Todo esto porque la edu-ciaa-fpga no tiene tanta memoria. Podría utilizar una zynq, quizás más adelante...

Respecto a las datasheets, las puse todas en https://github.com/cpantel/lvds/doc, me falta encontrar en estas o en alguna que me falte lo específico de iCE40HX4K en relación a edu-ciaa-fpga.

Gracias a lo que ya me fuiste guiando y habiéndome familiarizado más con el problema, he hecho algunos avances:

*) entiendo de la nota al pié de la página 2-9, tabla 2-8 que dice " These interfaces can be emulated with external resistors in all devices." que es... justo, lo que dice, que podría con unas resistencias y el verilog apropiado, siendo outputs generar los pares diferenciales que quiera, ¿es ok? Lo que me hace ruido es esos 1.2, 1.8, 2.5, 3.3 (te recuerdo que mis conocimientos de electrónica en general y analógica en particular son muy precarios, siendo generoso) , si fuera tan solo cambiar valores de resistencias, ¿para qué dice los voltajes?

*) Lo que dice del clock HSD100IFW1-A00_HannStar.pdf en las páginas 15-16, con RCLK (7t) min 39 Mhz, como en RXIN0-2 hay seis transiciones, estaríamos hablando de necesitar en algún lado un clock 39 x 6 = 234 Mhz, correcto? De ser así, casi que podría abandonar ya el proyecto pues aunque entiendo que según página 3-11 asumiendo que es posible emular los ouputs pares diferenciales estaría en el rango, no tengo instrumental para diagnosticar, mi osciloscopio llega a 100Mhz, ahí quizás si alguien tiene una edu-ciaa-fpga e instrumental, le manguearía que pruebe...

*) Para el clock antes tendría que terminar un proyecto previo, que es generar una señal VGA, ya he hecho el hardware (https://seguridad-agile.blogspot.com/2020/09/mi-segundo-pmod-dual-pmod-vga.html), me faltaba el clock y pegarle al verilog que tengo hasta que ande. Me parece que voy ir por este camino:

- Deuda con la vida

- Señal de ajuste por VGA, implica el clock, que lo puedo sacar de icicle o quizás leyendo FPGA-TN-02052-1-4-iCE40-sysCLOCK-PLL-Design-User-Guide.pdf

- Caracteres por VGA, lo arcaico

- Caracteres por VGA desde icicle (si entra..., https://github.com/cpantel/evilCodeSequence) -> módulo video

- Lo propio de este proyecto

- Ver que tan algo puede ir el clock

- Ver si se pueden implementar las señales LVDS a ciegas

- Reemplazar módulo video VGA por LVDS en icicle (si entra...)

*) respecto a 30 vs 32, claro, conté las pistas, no los pines en el conector, luego reviso bien

Mientras sigo mirando fijo el asunto de LVDS para que siga fermentando...

Gracias otra vez y saludos

[1] https://8bitworkshop.com/v3.9.0/?file=chardisplay.v&platform=verilog#, si alguien tiene ganas de divertirse, tocando digits.v se puede completar a-f para que muestre todo, lo dejo en base64 para no spoilear...

ICA3J28xMjA6IGJpdHMgPSA1J2IxMTExMTsKICAgICAgNydvMTIxOiBiaXRzID0gNSdiMDAwMDE7

CiAgICAgIDcnbzEyMjogYml0cyA9IDUnYjExMTExOwogICAgICA3J28xMjM6IGJpdHMgPSA1J2Ix

MDAwMTsKICAgICAgNydvMTI0OiBiaXRzID0gNSdiMTExMTE7CiAgICAgIAogICAgICA3J28xMzA6

IGJpdHMgPSA1J2IxMDAwMDsKICAgICAgNydvMTMxOiBiaXRzID0gNSdiMTAwMDA7CiAgICAgIDcn

bzEzMjogYml0cyA9IDUnYjExMTExOwogICAgICA3J28xMzM6IGJpdHMgPSA1J2IxMDAwMTsKICAg

ICAgNydvMTM0OiBiaXRzID0gNSdiMTExMTE7ICAgICAgCgogICAgICA3J28xNDA6IGJpdHMgPSA1

J2IwMDAwMDsKICAgICAgNydvMTQxOiBiaXRzID0gNSdiMDAwMDA7CiAgICAgIDcnbzE0MjogYml0

cyA9IDUnYjExMTExOwogICAgICA3J28xNDM6IGJpdHMgPSA1J2IxMDAwMDsKICAgICAgNydvMTQ0

OiBiaXRzID0gNSdiMTExMTE7ICAgICAgCiAgICAgIAogICAgICA3J28xNTA6IGJpdHMgPSA1J2Iw

MDAwMTsKICAgICAgNydvMTUxOiBiaXRzID0gNSdiMDAwMDE7CiAgICAgIDcnbzE1MjogYml0cyA9

IDUnYjExMTExOwogICAgICA3J28xNTM6IGJpdHMgPSA1J2IxMDAwMTsKICAgICAgNydvMTU0OiBi

aXRzID0gNSdiMTExMTE7CiAgICAgIAogICAgICA3J28xNjA6IGJpdHMgPSA1J2IxMTExMTsKICAg

ICAgNydvMTYxOiBiaXRzID0gNSdiMTAwMDE7CiAgICAgIDcnbzE2MjogYml0cyA9IDUnYjExMTEx

OwogICAgICA3J28xNjM6IGJpdHMgPSA1J2IxMDAwMDsKICAgICAgNydvMTY0OiBiaXRzID0gNSdi

MTExMTE7CgogICAgICA3J28xNzA6IGJpdHMgPSA1J2IxMTExMTsKICAgICAgNydvMTcxOiBiaXRz

ID0gNSdiMTAwMDA7CiAgICAgIDcnbzE3MjogYml0cyA9IDUnYjExMTExOwogICAgICA3J28xNzM6

IGJpdHMgPSA1J2IxMDAwMDsKICAgICAgNydvMTc0OiBiaXRzID0gNSdiMTAwMDA7Cg==

CiAgICAgIDcnbzEyMjogYml0cyA9IDUnYjExMTExOwogICAgICA3J28xMjM6IGJpdHMgPSA1J2Ix

MDAwMTsKICAgICAgNydvMTI0OiBiaXRzID0gNSdiMTExMTE7CiAgICAgIAogICAgICA3J28xMzA6

IGJpdHMgPSA1J2IxMDAwMDsKICAgICAgNydvMTMxOiBiaXRzID0gNSdiMTAwMDA7CiAgICAgIDcn

bzEzMjogYml0cyA9IDUnYjExMTExOwogICAgICA3J28xMzM6IGJpdHMgPSA1J2IxMDAwMTsKICAg

ICAgNydvMTM0OiBiaXRzID0gNSdiMTExMTE7ICAgICAgCgogICAgICA3J28xNDA6IGJpdHMgPSA1

J2IwMDAwMDsKICAgICAgNydvMTQxOiBiaXRzID0gNSdiMDAwMDA7CiAgICAgIDcnbzE0MjogYml0

cyA9IDUnYjExMTExOwogICAgICA3J28xNDM6IGJpdHMgPSA1J2IxMDAwMDsKICAgICAgNydvMTQ0

OiBiaXRzID0gNSdiMTExMTE7ICAgICAgCiAgICAgIAogICAgICA3J28xNTA6IGJpdHMgPSA1J2Iw

MDAwMTsKICAgICAgNydvMTUxOiBiaXRzID0gNSdiMDAwMDE7CiAgICAgIDcnbzE1MjogYml0cyA9

IDUnYjExMTExOwogICAgICA3J28xNTM6IGJpdHMgPSA1J2IxMDAwMTsKICAgICAgNydvMTU0OiBi

aXRzID0gNSdiMTExMTE7CiAgICAgIAogICAgICA3J28xNjA6IGJpdHMgPSA1J2IxMTExMTsKICAg

ICAgNydvMTYxOiBiaXRzID0gNSdiMTAwMDE7CiAgICAgIDcnbzE2MjogYml0cyA9IDUnYjExMTEx

OwogICAgICA3J28xNjM6IGJpdHMgPSA1J2IxMDAwMDsKICAgICAgNydvMTY0OiBiaXRzID0gNSdi

MTExMTE7CgogICAgICA3J28xNzA6IGJpdHMgPSA1J2IxMTExMTsKICAgICAgNydvMTcxOiBiaXRz

ID0gNSdiMTAwMDA7CiAgICAgIDcnbzE3MjogYml0cyA9IDUnYjExMTExOwogICAgICA3J28xNzM6

IGJpdHMgPSA1J2IxMDAwMDsKICAgICAgNydvMTc0OiBiaXRzID0gNSdiMTAwMDA7Cg==

Pablo A. Llanos

Jun 20, 2022, 12:31:35 PM6/20/22

to embeb...@googlegroups.com

Hola Carlos,

No pude acceder a los datasheets con el link que compartiste pero finalmente logré encontrarlos en tu perfil y creo que el link correcto es https://github.com/cpantel/lvds/tree/master/doc

Después de una lectura rápida de las Notas Técnicas y del Datasheet mis conclusiones son las siguientes:

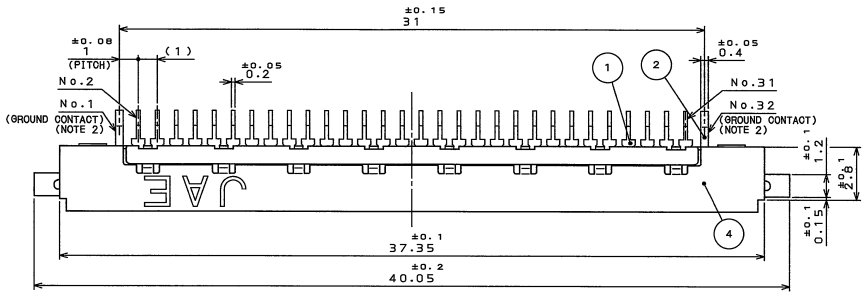

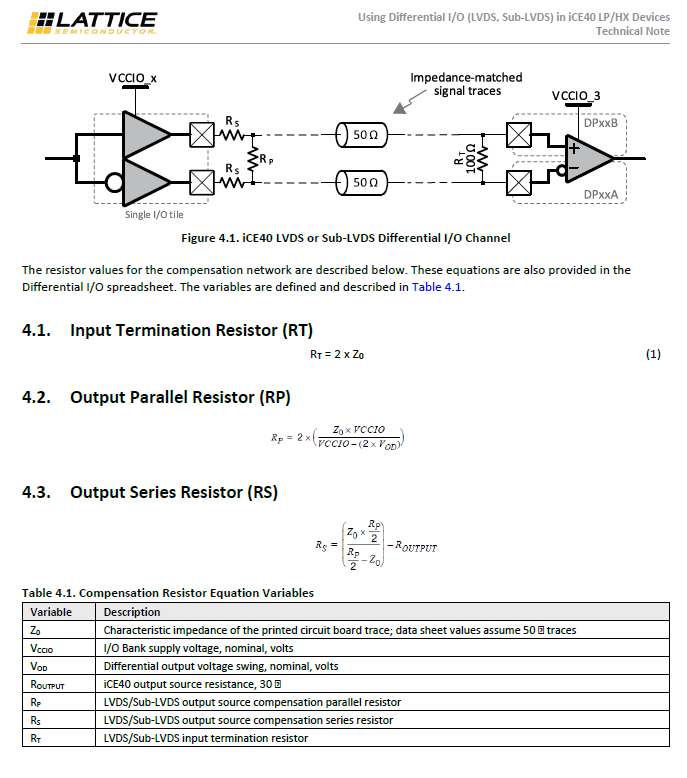

*) entiendo de la nota al pié de la página 2-9, tabla 2-8 que dice " These interfaces can be emulated with external resistors in all devices." que es... justo, lo que dice, que podría con unas resistencias y el verilog apropiado, siendo outputs generar los pares diferenciales que quiera, ¿es ok? Lo que me hace ruido es esos 1.2, 1.8, 2.5, 3.3 (te recuerdo que mis conocimientos de electrónica en general y analógica en particular son muy precarios, siendo generoso) , si fuera tan solo cambiar valores de resistencias, ¿para qué dice los voltajes?

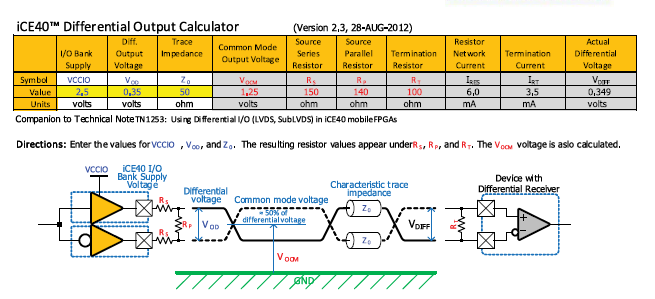

El FPGA utiliza dos pares de GPIOs y una red de resistencias para emular una salida diferencial. En la Nota Técnica FPGA-TN-02213-1-7 especifica las fórmulas para calcular los valores de las resistencias de la red, de hecho el ejemplo en la página 8 tiene exactamente los valores que necesitas:

El voltaje del banco de GPIOs del FPGA debe ser de 2.5V (para lograr el offset que especifica el datasheet del display: 1.25V Typ), el display también especifica un voltaje diferencial mínimo de 100mV y máximo de 600mV, por lo que 350mV es un valor típico y recomendable, la impedancia single-ended de cada pista es 50 ohm y diferencial de 100 ohm; tomando esos parámetros de entrada el valor de las resistencias serie (Rs) sería de 150 ohm y de la resistencia paralela (Rp) de 140 ohm.

*) Lo que dice del clock HSD100IFW1-A00_HannStar.pdf en las páginas 15-16, con RCLK (7t) min 39 Mhz, como en RXIN0-2 hay seis transiciones, estaríamos hablando de necesitar en algún lado un clock 39 x 6 = 234 Mhz, correcto? De ser así, casi que podría abandonar ya el proyecto pues aunque entiendo que según página 3-11 asumiendo que es posible emular los ouputs pares diferenciales estaría en el rango, no tengo instrumental para diagnosticar, mi osciloscopio llega a 100Mhz, ahí quizás si alguien tiene una edu-ciaa-fpga e instrumental, le manguearía que pruebe...

El clock es de 45 MHz, como nada es perfecto y siempre hay un margen de error, la hoja de datos establece el clock mínimo y máximo que tolera (39 y 51.42 MHz, respectivamente). Si utilizas el mínimo de 39 MHz, cualquier desviación en los timmings provocará errores en el controlador del TFT, así que debes utilizar 45 MHz como frecuencia de clock.

En cada ciclo de clock hay 7 transiciones (no 6); son 18 bits de datos del pixel, más 3 bits de control (DE, VS y HS) repartidos en 3 pares diferenciales: 3 * 6 + 3 = 21 => 21 / 3 = 7, lo que implica un pixel clock de 315 MHz. El framebuffer precisamente se utiliza para poder usar DMA o cualquier otro artilugio de hardware para generar las señales, los clocks son bastante altos como para realizar operaciones o transformaciones con píxeles.

*) respecto a 30 vs 32, claro, conté las pistas, no los pines en el conector, luego reviso bien

En la hoja de datos, los TFT siempre mencionan el conector que utilizan, en el caso de este TFT en la página donde especifica el pinout está el part number del conector. Si buscas el datasheet del conector te puedes ahorrar un par de dolores de cabeza.

CN1 (Input signal): FI-XB30SSRL-HF16 (JAE or equivalent)

No es fácil lo que estás intentando hacer, cuando trabajas con un LCD de 16x2 caracteres las señales son de muy baja velocidad y no presenta grandes desafíos. A mayor velocidad (como es el caso de este tipo de bus, bus de memorias DDR, PCIe, etc), la complejidad aumenta rápidamente y debes tener en cuenta muchas cosas más que cuando trabajas con señales de baja velocidad. Lo ideal sería que cuentes con instrumental para chequear la integridad de las señales en caso que tengas que disgnosticar algún problema, por ejemplo: reflejo de la señal, crosstalk, etc.

Espero que te sirva la info y éxitos con el proyecto!

Saludos cordiales,

Pablo Llanos Clariá

Embedded Linux Expert

UNITED CODERS

Para ver esta conversación en el sitio web, visita https://groups.google.com/d/msgid/embebidos32/70890135-7511-4e8f-9929-dd504914b04cn%40googlegroups.com.

Carlos Pantelides

Jun 20, 2022, 2:13:18 PM6/20/22

to Embebidos32

ok, ahí había revisado y que era por 7 y no 6 y agregándole lo que decís que mejor 45, 315, ok, estoy indudablemente afuera.

Durante un momento tuve un rayito de esperanza, pensé que si nos contentamos con monocromo no haría falta estar transmitiendo cada bit, con prender los siete o apagarlos a 45 Mhz funcionaría, pero luego me percaté de que HS y VS ( y DE que me falta identificar) son parte de los bits

Si en lugar de

g[0], r[5], r[4], r[3], r[2], r[1], r[0]

b[1], b[0], g[5], g[4], g[3], g[2], g[1]

de, vs , hs , b[5], b[4], b[3], b[2]

b[1], b[0], g[5], g[4], g[3], g[2], g[1]

de, vs , hs , b[5], b[4], b[3], b[2]

fuera

de, g[0], r[5], r[4], r[3], r[2], r[1]

vs, b[1], b[0], g[5], g[4], g[3], g[2]

hs, b[5], b[4], b[3], b[2], r[0], g[1]

vs, b[1], b[0], g[5], g[4], g[3], g[2]

hs, b[5], b[4], b[3], b[2], r[0], g[1]

con 90Mhz podría hacerse un hack, ¿estoy muy equivocado?

El premio consuelo será haber aprendido algo de modo teórico...

Muchas gracias por el intento.

Saludos

Has recibido este mensaje porque estás suscrito a un tema del grupo "Embebidos32" de Grupos de Google.

Para cancelar la suscripción a este tema, visita https://groups.google.com/d/topic/embebidos32/2GWZL2_qXVo/unsubscribe.

Para cancelar la suscripción a este grupo y a todos sus temas, envía un correo electrónico a embebidos32...@googlegroups.com.

Para ver esta conversación en el sitio web, visita https://groups.google.com/d/msgid/embebidos32/CAFvB5gN%2Bi6yXMt0BXuEGxP2XTq3MeHouTqG47BscetvnnEmitA%40mail.gmail.com.

Pablo A. Llanos

Jun 20, 2022, 2:50:47 PM6/20/22

to embeb...@googlegroups.com

Lamentablemente no hay muchos hacks posibles porque el controlador del TFT tiene timings que deben ser bastante precisos. Hace un tiempo, tuve que solucionar un problema similar (un cliente de China que quería usar un TFT de 8", 16.7M de colores, con un microcontrolador del paleolítico), la solución fue utilizar un IC

RA8876M de una empresa Taiwanesa que tiene una SDRAM embebida. No podrás utilizar exactamente ese part number porque en nuestro caso el TFT tenía una interfaz TTL RGB y no LVDS, pero recuerdo que el mismo fabricante tenía otros IC que trabajaban con LVDS.

Si utilizas un driver como el RA8876M podrías transferir los datos mediantes SPI o un puerto paralelo, el controlador tiene varios modos de memoria, como por ejemplo, reemplazar sólo los pixels que cambian y no toda la memoria del buffer, modo consola de texto (como el que estás intentando implementar), un motor para dibujar, etc.

Otra alternativa es buscar paneles que ya traen un controlador con interfaz SPI o paralela (8080 o 6800), como por ejemplo éste

Si la intención era reutilizar ese panel de laptop, me temo que con la memoria del FPGA sólo puedes mostrar una imagen estática.

Saludos cordiales,

Para ver esta conversación en el sitio web, visita https://groups.google.com/d/msgid/embebidos32/CA%2BPxht2QqmNotwOhdnDS8MyV1c0rrGxNnvO%2BH3tUF9B1zpGF3Q%40mail.gmail.com.

Carlos Pantelides

Jul 19, 2022, 9:46:26 PM7/19/22

to Embebidos32

Para compensar la frustración de no poder hacer nada con la pantalla, comparto que si pude reutilizar la webcam, la verdad es que fue relativamente sencillo.

Saludos

Reply all

Reply to author

Forward

0 new messages