Negedge async reset?

45 views

Skip to first unread message

Øyvind Harboe

Apr 9, 2023, 5:17:45 PM4/9/23

to chisel-users

Silly question: can Chisel generate a negedge async reset?

I.e. can Chisel generate:

always @(posedge clock or negedge reset) begin

if (!reset) begin

if (!reset) begin

....

Øyvind Harboe

Apr 10, 2023, 4:03:43 AM4/10/23

to chisel-users

I searched the Chisel3 and FIRRTL code and I can't find any "negedge" code.

Indeed, it looks like "posedge" is hardcoded into Chisel.

Øyvind Harboe

Apr 11, 2023, 5:09:55 AM4/11/23

to chisel-users

If I do this, then the sensitivity on the reset signal is removed:

Alin Parcalab

Apr 11, 2023, 2:19:41 PM4/11/23

to chisel...@googlegroups.com

Just invert the signal.

--

You received this message because you are subscribed to the Google Groups "chisel-users" group.

To unsubscribe from this group and stop receiving emails from it, send an email to chisel-users...@googlegroups.com.

To view this discussion on the web visit https://groups.google.com/d/msgid/chisel-users/3942ce6e-853a-4afa-835d-5c6aa66aabdbn%40googlegroups.com.

Message has been deleted

Message has been deleted

Message has been deleted

Øyvind Harboe

Apr 13, 2023, 1:42:20 AM4/13/23

to chisel-users

LLVM CIRCT can do this.

(Strange, it says "message deleted" in the groups GUI, trying a repost)

On Sunday, April 9, 2023 at 11:17:45 PM UTC+2 Øyvind Harboe wrote:

Øyvind Harboe

Apr 13, 2023, 2:59:32 AM4/13/23

to chisel-users

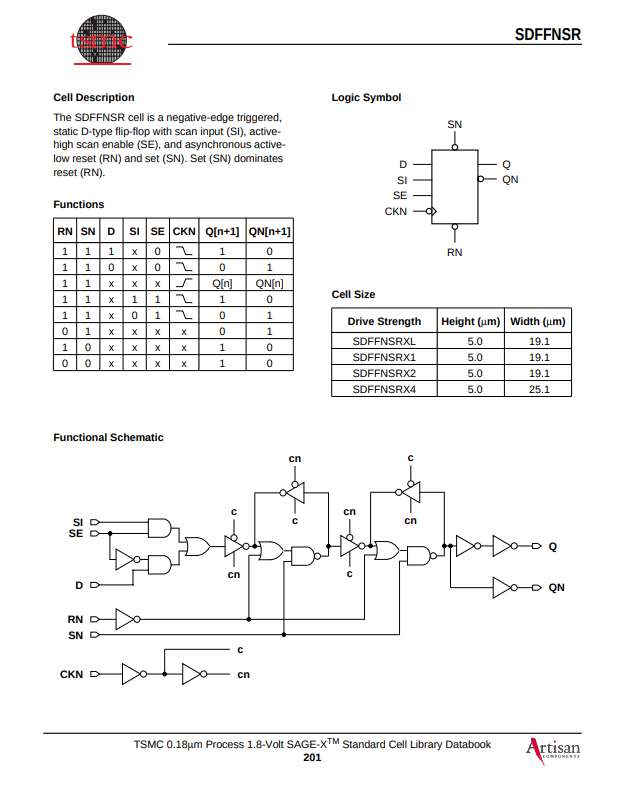

Some more motivation on supporting async negedge from Chisel directly.

This PDK, and I'm sure lots of others, use async negedge for primitives directly, so if Chisel can output async negedge code from reset agnostic code, that can help reduce FUD (https://en.wikipedia.org/wiki/Fear,_uncertainty,_and_doubt) about Chisel.

On Sunday, April 9, 2023 at 11:17:45 PM UTC+2 Øyvind Harboe wrote:

Schuyler Eldridge

Apr 13, 2023, 12:36:03 PM4/13/23

to chisel...@googlegroups.com

Thanks for providing more information here, Oyvind.

Yes, we have support in the lower level portions of CIRCT. Hardware/SystemVerilog Dialects can represent and emit negedge reset. We have not provided a way to get to this from a Chisel API, though. We should be able to get this online relatively easily. The only question is how the Chisel API should look.

--

You received this message because you are subscribed to the Google Groups "chisel-users" group.

To unsubscribe from this group and stop receiving emails from it, send an email to chisel-users...@googlegroups.com.

To view this discussion on the web visit https://groups.google.com/d/msgid/chisel-users/7e421038-4e62-4214-9e5a-7faa4ebf76bfn%40googlegroups.com.

Kevin Laeufer

Apr 13, 2023, 12:52:48 PM4/13/23

to chisel...@googlegroups.com

Maybe Chisel wouldn’t actually need an API expansion, if the compiler could just propagate a negation an a AsyncReset signal into the register.

That way everything should “just work” and you can take a design that uses standard reset polarity and convert it to inverted reset polarity without changing any code inside. You just invert the reset signal that is being fed into the design (or mark the top level input as a low-active reset which would require a small API expansion) and then you are done.

Kevin

Sent from my iPhone

On Apr 13, 2023, at 12:36, Schuyler Eldridge <schuyler...@gmail.com> wrote:

Thanks for providing more information here, Oyvind.Yes, we have support in the lower level portions of CIRCT. Hardware/SystemVerilog Dialects can represent and emit negedge reset. We have not provided a way to get to this from a Chisel API, though. We should be able to get this online relatively easily. The only question is how the Chisel API should look.

On Thu, Apr 13, 2023 at 2:59 AM Øyvind Harboe <oyvind...@gmail.com> wrote:

Some more motivation on supporting async negedge from Chisel directly.This PDK, and I'm sure lots of others, use async negedge for primitives directly, so if Chisel can output async negedge code from reset agnostic code, that can help reduce FUD (https://en.wikipedia.org/wiki/Fear,_uncertainty,_and_doubt) about Chisel.

https://classes.engineering.wustl.edu/permanant/cse260m/images/9/95/Tsmc18_component.pdf<Screenshot from 2023-04-13 08-57-48.png>

--On Sunday, April 9, 2023 at 11:17:45 PM UTC+2 Øyvind Harboe wrote:Silly question: can Chisel generate a negedge async reset?I.e. can Chisel generate:always @(posedge clock or negedge reset) begin

if (!reset) begin....

You received this message because you are subscribed to the Google Groups "chisel-users" group.

To unsubscribe from this group and stop receiving emails from it, send an email to chisel-users...@googlegroups.com.

To view this discussion on the web visit https://groups.google.com/d/msgid/chisel-users/7e421038-4e62-4214-9e5a-7faa4ebf76bfn%40googlegroups.com.

--

You received this message because you are subscribed to the Google Groups "chisel-users" group.

To unsubscribe from this group and stop receiving emails from it, send an email to chisel-users...@googlegroups.com.

To view this discussion on the web visit https://groups.google.com/d/msgid/chisel-users/CAG%3DZR1uG6G%2BQi-2zRoe-YPX_bk2vvBqJtrmcZK6Kt35zha87gA%40mail.gmail.com.

Øyvind Harboe

Apr 13, 2023, 1:08:35 PM4/13/23

to chisel...@googlegroups.com

Thanks!

You received this message because you are subscribed to a topic in the Google Groups "chisel-users" group.

To unsubscribe from this topic, visit https://groups.google.com/d/topic/chisel-users/Q1jgdcnIf6w/unsubscribe.

To unsubscribe from this group and all its topics, send an email to chisel-users...@googlegroups.com.

To view this discussion on the web visit https://groups.google.com/d/msgid/chisel-users/CAG%3DZR1uG6G%2BQi-2zRoe-YPX_bk2vvBqJtrmcZK6Kt35zha87gA%40mail.gmail.com.

Jack Koenig

Apr 14, 2023, 1:41:01 PM4/14/23

to chisel...@googlegroups.com

Sorry for some of the delayed messages everyone, Google Group's spam detection is really doing a garbage job right now. As you can probably see there are 3 messages, 2 from Øyvind and 1 from Warren that just went out. They were sent 1-2 days ago potentially before some other messages that were not blocked so the ordering is a bit weird.

I have tried to relax the spam filtering (especially because it keeps filtering long-time members of this group which makes zero sense), but as far as I can tell, this is not possible: https://support.google.com/groups/thread/132457606/messages-held-in-moderation-despite-no-moderation-and-anyone-on-the-web-posting-settings?hl=en

Perhaps there's a lot of spam happening behind the scenes that I never see as a moderator and this is the price we pay, but in any case, sorry about this issue. I will continue to try to check for blocked messages more frequently.

On Fri, Apr 14, 2023 at 10:26 AM Øyvind Harboe <oyvind...@gmail.com> wrote:

This side-steps the ask. The problem I'm facing is that I'm being asked to generate Verilog in a particular form. I don't want to give pushback on the exact form requested, especially if it isn't an important difference. I just want to provide what was asked for. This will help smooth things along in Chisel adoption.LLVM CIRCT does support negedge async reset, but FIRRTL does not, as I understand it: https://discourse.llvm.org/t/can-llvm-circt-output-negedge-async-reset/69891/2

To view this discussion on the web visit https://groups.google.com/d/msgid/chisel-users/8307e72c-ebb9-43db-9360-54c60002ae0an%40googlegroups.com.

Øyvind Harboe

Apr 14, 2023, 1:45:54 PM4/14/23

to chisel...@googlegroups.com

Thanks!

On Fri, Apr 14, 2023 at 7:26 PM Warren Savage <warren...@rocksavage.tech> wrote:

As Alin says, you can just add an inverter if needed. In my experience, it doesn't really matter and the reset net will need to be heavily buffered in the final chip netlist, which is best done with inverters anyway.There is a nice writeup on resets here from the Chisel docs: https://www.chisel-lang.org/chisel3/docs/explanations/reset.htmlWarren

You received this message because you are subscribed to a topic in the Google Groups "chisel-users" group.

To unsubscribe from this topic, visit https://groups.google.com/d/topic/chisel-users/Q1jgdcnIf6w/unsubscribe.

To unsubscribe from this group and all its topics, send an email to chisel-users...@googlegroups.com.

To view this discussion on the web visit https://groups.google.com/d/msgid/chisel-users/f403797c-69d4-4632-afe1-0affc3f91737n%40googlegroups.com.

Øyvind Harboe

+4791786146

+4791786146

Jack Koenig

Apr 14, 2023, 1:50:17 PM4/14/23

to chisel...@googlegroups.com

I generally agree that inverting the reset is fine and works in practice (that's what we do) but Øyvind's point that emitting Verilog in the form people want/expect does help reduce FUD.

The only issue I see is development effort. I don't think it's that hard but as with most things it's a zero-sum game of time vs. other development.

I do think this should be reflected in Chisel with sensitivity as a parameter on the AsyncReset type (and the same thing can be applied to Clocks). Basically `AsyncReset()` becomes an alias for `AsyncReset(Posedge)` and there is also `AsyncReset(Negedge)`. This can be represented basically the same way as FIRRTL and should integrate trivially into existing reset inference. Currently we do not define any ops on AsyncReset, we could then define inversion which would have the effect of inverting the sensitive, ie. ~AsyncReset(Posedge) == AsyncReset(Negedge), thus no actual inversions need to show up in the Verilog (unless you cast an AsyncReset(Negedge) to Bool, then an actual Verilog inversion will be materialized).

On Fri, Apr 14, 2023 at 10:26 AM Øyvind Harboe <oyvind...@gmail.com> wrote:

This side-steps the ask. The problem I'm facing is that I'm being asked to generate Verilog in a particular form. I don't want to give pushback on the exact form requested, especially if it isn't an important difference. I just want to provide what was asked for. This will help smooth things along in Chisel adoption.LLVM CIRCT does support negedge async reset, but FIRRTL does not, as I understand it: https://discourse.llvm.org/t/can-llvm-circt-output-negedge-async-reset/69891/2

On Tuesday, April 11, 2023 at 8:19:41 PM UTC+2 alinpa...@gmail.com wrote:

To view this discussion on the web visit https://groups.google.com/d/msgid/chisel-users/8307e72c-ebb9-43db-9360-54c60002ae0an%40googlegroups.com.

Øyvind Harboe

Apr 14, 2023, 1:59:21 PM4/14/23

to chisel-users

I find that engineering is almost always easier and cheaper as a solution for this sort of thing any non-engineering solutions(training, documentation, enticing, evangalizing, etc.).

Even for those that write Verilog only, there is an enormously strong push to stay on the straight and narrow: only synchronous positively edge triggered logic. The tools really like this so it is an economical and safe path. Because of this, there is very little Verilog that I can't demonstrate in Chisel, where the QoR (quality of results in from synthesis to GDS II) isn't just about the same.

I may post some specific studies of manual Verilog vs Chisel later on as a result of some discussions we had... This is where async vs. synchronous reset came up and I discovered that Chisel is reset type agnostic. In my designs I only ever needed synchronous reset.

Which is why I take the stance: show me the Verilog and I'll show you the Chisel.

Worst case, I have to admit that there is some kind of Verilog that Chisel can't do. This rarely makes the listener unhappy and unwilling to hear about Chisel in the future...

Even for those that write Verilog only, there is an enormously strong push to stay on the straight and narrow: only synchronous positively edge triggered logic. The tools really like this so it is an economical and safe path. Because of this, there is very little Verilog that I can't demonstrate in Chisel, where the QoR (quality of results in from synthesis to GDS II) isn't just about the same.

I may post some specific studies of manual Verilog vs Chisel later on as a result of some discussions we had... This is where async vs. synchronous reset came up and I discovered that Chisel is reset type agnostic. In my designs I only ever needed synchronous reset.

Kevin Laeufer

Apr 14, 2023, 2:06:15 PM4/14/23

to chisel...@googlegroups.com

Hi Øyvind,

If you have any examples where you actually get a worse netlist from

Chisel than you can get from Verilog I would be very interested in that

as I am currently trying to study if there is any way we could improve

QoR by adding new primitives to Chisel. Whether the bad Chisel QoR is

because of missing 'X', unique case, missing FSM extraction etc. does

not matter. Please send anything you can publicly share to my email address.

Best,

Kevin

> https://discourse.llvm.org/t/can-llvm-circt-output-negedge-async-reset/69891/2 <https://discourse.llvm.org/t/can-llvm-circt-output-negedge-async-reset/69891/2>

If you have any examples where you actually get a worse netlist from

Chisel than you can get from Verilog I would be very interested in that

as I am currently trying to study if there is any way we could improve

QoR by adding new primitives to Chisel. Whether the bad Chisel QoR is

because of missing 'X', unique case, missing FSM extraction etc. does

not matter. Please send anything you can publicly share to my email address.

Best,

Kevin

>

> On Tuesday, April 11, 2023 at 8:19:41 PM UTC+2

> alinpa...@gmail.com wrote:

>

> Just invert the signal.

>

> On 11.04.2023 12:09, Øyvind Harboe wrote:

>> If I do this, then the sensitivity on the reset signal is

>> removed:

>>

>> https://scastie.scala-lang.org/oWTQ3z9BSSKtkkJY26POLw

>> <https://scastie.scala-lang.org/oWTQ3z9BSSKtkkJY26POLw>

>>

>>

>>

>> On Monday, April 10, 2023 at 10:03:43 AM UTC+2 Øyvind

>> Harboe wrote:

>>

>> I searched the Chisel3 and FIRRTL code and I can't

>> find any "negedge" code.

>>

>> Indeed, it looks like "posedge" is hardcoded into Chisel.

>>

>>

>> https://github.com/chipsalliance/firrtl/blob/57b8a395ee8d5fdabb2deed3db7d0c644f0a7eed/src/main/scala/firrtl/backends/verilog/VerilogEmitter.scala#L1214 <https://github.com/chipsalliance/firrtl/blob/57b8a395ee8d5fdabb2deed3db7d0c644f0a7eed/src/main/scala/firrtl/backends/verilog/VerilogEmitter.scala#L1214>

> On Tuesday, April 11, 2023 at 8:19:41 PM UTC+2

> alinpa...@gmail.com wrote:

>

> Just invert the signal.

>

> On 11.04.2023 12:09, Øyvind Harboe wrote:

>> If I do this, then the sensitivity on the reset signal is

>> removed:

>>

>> https://scastie.scala-lang.org/oWTQ3z9BSSKtkkJY26POLw

>> <https://scastie.scala-lang.org/oWTQ3z9BSSKtkkJY26POLw>

>>

>>

>>

>> On Monday, April 10, 2023 at 10:03:43 AM UTC+2 Øyvind

>> Harboe wrote:

>>

>> I searched the Chisel3 and FIRRTL code and I can't

>> find any "negedge" code.

>>

>> Indeed, it looks like "posedge" is hardcoded into Chisel.

>>

>>

>>

>> On Sunday, April 9, 2023 at 11:17:45 PM UTC+2 Øyvind

>> Harboe wrote:

>>

>> Silly question: can Chisel generate a negedge

>> async reset?

>>

>> https://scastie.scala-lang.org/5uLlh1IqSuWRYCg9mFCA1w <https://scastie.scala-lang.org/5uLlh1IqSuWRYCg9mFCA1w>

>> On Sunday, April 9, 2023 at 11:17:45 PM UTC+2 Øyvind

>> Harboe wrote:

>>

>> Silly question: can Chisel generate a negedge

>> async reset?

>>

>>

>> I.e. can Chisel generate:

>>

>>

>> always @(posedge clock or negedge reset) begin

>> if (!reset) begin

>> ....

>>

>> --

>> You received this message because you are subscribed to

>> the Google Groups "chisel-users" group.

>> To unsubscribe from this group and stop receiving emails

>> from it, send an email to chisel-users...@googlegroups.com.

>> To view this discussion on the web visit

>> https://groups.google.com/d/msgid/chisel-users/3942ce6e-853a-4afa-835d-5c6aa66aabdbn%40googlegroups.com <https://groups.google.com/d/msgid/chisel-users/3942ce6e-853a-4afa-835d-5c6aa66aabdbn%40googlegroups.com?utm_medium=email&utm_source=footer>.

>> I.e. can Chisel generate:

>>

>>

>> always @(posedge clock or negedge reset) begin

>> if (!reset) begin

>> ....

>>

>> --

>> You received this message because you are subscribed to

>> the Google Groups "chisel-users" group.

>> To unsubscribe from this group and stop receiving emails

>> from it, send an email to chisel-users...@googlegroups.com.

>> To view this discussion on the web visit

>

> --

> You received this message because you are subscribed to the

> Google Groups "chisel-users" group.

> To unsubscribe from this group and stop receiving emails from

> it, send an email to chisel-users...@googlegroups.com.

>

> To view this discussion on the web visit

> https://groups.google.com/d/msgid/chisel-users/8307e72c-ebb9-43db-9360-54c60002ae0an%40googlegroups.com <https://groups.google.com/d/msgid/chisel-users/8307e72c-ebb9-43db-9360-54c60002ae0an%40googlegroups.com?utm_medium=email&utm_source=footer>.

> --

> You received this message because you are subscribed to the

> Google Groups "chisel-users" group.

> To unsubscribe from this group and stop receiving emails from

> it, send an email to chisel-users...@googlegroups.com.

>

> To view this discussion on the web visit

>

> --

> You received this message because you are subscribed to the Google

> Groups "chisel-users" group.

> To unsubscribe from this group and stop receiving emails from it, send

> an email to chisel-users...@googlegroups.com

> <mailto:chisel-users...@googlegroups.com>.

> --

> You received this message because you are subscribed to the Google

> Groups "chisel-users" group.

> To unsubscribe from this group and stop receiving emails from it, send

> an email to chisel-users...@googlegroups.com

> To view this discussion on the web visit

> https://groups.google.com/d/msgid/chisel-users/67bb7c85-dd43-450d-86c1-df5af471c500n%40googlegroups.com <https://groups.google.com/d/msgid/chisel-users/67bb7c85-dd43-450d-86c1-df5af471c500n%40googlegroups.com?utm_medium=email&utm_source=footer>.

Øyvind Harboe

Apr 14, 2023, 2:08:42 PM4/14/23

to chisel...@googlegroups.com

Will do!

You received this message because you are subscribed to a topic in the Google Groups "chisel-users" group.

To unsubscribe from this topic, visit https://groups.google.com/d/topic/chisel-users/Q1jgdcnIf6w/unsubscribe.

To unsubscribe from this group and all its topics, send an email to chisel-users...@googlegroups.com.

To view this discussion on the web visit https://groups.google.com/d/msgid/chisel-users/ff2d4fdf-7eb5-df15-b1aa-3d7d64245b31%40berkeley.edu.

Øyvind Harboe

Apr 19, 2023, 6:10:55 AM4/19/23

to chisel-users

Reply all

Reply to author

Forward

0 new messages