Method to compare Chisel vs. manually written Verilog

41 views

Skip to first unread message

Øyvind Harboe

Apr 17, 2023, 5:21:25 AM4/17/23

to chisel-users

The example is a simple statemachine that detects 0xdeadbeef.

In this post, I want to show a method to compare quality of results, not bottom out on how to write Chisel.

Commercial tools and PDKs are under NDA, so here I'm using OpenROAD-flow-scripts to generate numbers.

Note that the Chisel and SystemVerilog is not semantically identical here. However, this is a realistic example of the difference in result you get when you give Chisel to someone who has prior experience from SystemVerilog.

OpenROAD flow also provides timing as wella as area and other detail, but for now, let's look only at synthesis results.

Looking only at the synthesis results for Chisel below:

$ make DESIGN_CONFIG=designs/asap7/example/config.mk

$ cat reports/asap7/example/base/synth_stat.txt

24. Printing statistics.

=== Example ===

Number of wires: 76

Number of wire bits: 76

Number of public wires: 8

Number of public wire bits: 8

Number of memories: 0

Number of memory bits: 0

Number of processes: 0

Number of cells: 68

AND2x2_ASAP7_75t_R 2

AND3x1_ASAP7_75t_R 1

AND4x1_ASAP7_75t_R 1

AND5x1_ASAP7_75t_R 1

AO21x1_ASAP7_75t_R 3

BUFx2_ASAP7_75t_R 1

DFFLQNx1_ASAP7_75t_R 8

HAxp5_ASAP7_75t_R 4

INVx1_ASAP7_75t_R 13

NAND2x1_ASAP7_75t_R 5

NOR2x1_ASAP7_75t_R 1

OA211x2_ASAP7_75t_R 1

OA21x2_ASAP7_75t_R 8

OA22x2_ASAP7_75t_R 1

OAI21x1_ASAP7_75t_R 2

OAI22x1_ASAP7_75t_R 2

OR2x2_ASAP7_75t_R 1

OR3x1_ASAP7_75t_R 8

OR3x2_ASAP7_75t_R 1

OR4x1_ASAP7_75t_R 3

XNOR2x1_ASAP7_75t_R 1

Chip area for module '\Example': 7.741980

24. Printing statistics.

=== Example ===

Number of wires: 76

Number of wire bits: 76

Number of public wires: 8

Number of public wire bits: 8

Number of memories: 0

Number of memory bits: 0

Number of processes: 0

Number of cells: 68

AND2x2_ASAP7_75t_R 2

AND3x1_ASAP7_75t_R 1

AND4x1_ASAP7_75t_R 1

AND5x1_ASAP7_75t_R 1

AO21x1_ASAP7_75t_R 3

BUFx2_ASAP7_75t_R 1

DFFLQNx1_ASAP7_75t_R 8

HAxp5_ASAP7_75t_R 4

INVx1_ASAP7_75t_R 13

NAND2x1_ASAP7_75t_R 5

NOR2x1_ASAP7_75t_R 1

OA211x2_ASAP7_75t_R 1

OA21x2_ASAP7_75t_R 8

OA22x2_ASAP7_75t_R 1

OAI21x1_ASAP7_75t_R 2

OAI22x1_ASAP7_75t_R 2

OR2x2_ASAP7_75t_R 1

OR3x1_ASAP7_75t_R 8

OR3x2_ASAP7_75t_R 1

OR4x1_ASAP7_75t_R 3

XNOR2x1_ASAP7_75t_R 1

Chip area for module '\Example': 7.741980

$ cat reports/asap7/example/base/synth_stat.txt

24. Printing statistics.

=== Example ===

Number of wires: 53

Number of wire bits: 53

Number of public wires: 8

Number of public wire bits: 8

Number of memories: 0

Number of memory bits: 0

Number of processes: 0

Number of cells: 45

AND2x2_ASAP7_75t_R 1

AND3x1_ASAP7_75t_R 2

AND3x2_ASAP7_75t_R 1

AO21x1_ASAP7_75t_R 2

AO21x2_ASAP7_75t_R 1

AO22x2_ASAP7_75t_R 1

AO31x2_ASAP7_75t_R 1

AOI21x1_ASAP7_75t_R 2

BUFx6f_ASAP7_75t_R 1

DFFASRHQNx1_ASAP7_75t_R 6

HAxp5_ASAP7_75t_R 4

INVx1_ASAP7_75t_R 9

NAND2x1_ASAP7_75t_R 2

OA21x2_ASAP7_75t_R 1

OR3x1_ASAP7_75t_R 3

OR4x1_ASAP7_75t_R 4

TIEHIx1_ASAP7_75t_R 1

XNOR2x2_ASAP7_75t_R 2

XOR2x2_ASAP7_75t_R 1

Chip area for module '\Example': 6.065280

24. Printing statistics.

=== Example ===

Number of wires: 53

Number of wire bits: 53

Number of public wires: 8

Number of public wire bits: 8

Number of memories: 0

Number of memory bits: 0

Number of processes: 0

Number of cells: 45

AND2x2_ASAP7_75t_R 1

AND3x1_ASAP7_75t_R 2

AND3x2_ASAP7_75t_R 1

AO21x1_ASAP7_75t_R 2

AO21x2_ASAP7_75t_R 1

AO22x2_ASAP7_75t_R 1

AO31x2_ASAP7_75t_R 1

AOI21x1_ASAP7_75t_R 2

BUFx6f_ASAP7_75t_R 1

DFFASRHQNx1_ASAP7_75t_R 6

HAxp5_ASAP7_75t_R 4

INVx1_ASAP7_75t_R 9

NAND2x1_ASAP7_75t_R 2

OA21x2_ASAP7_75t_R 1

OR3x1_ASAP7_75t_R 3

OR4x1_ASAP7_75t_R 4

TIEHIx1_ASAP7_75t_R 1

XNOR2x2_ASAP7_75t_R 2

XOR2x2_ASAP7_75t_R 1

Chip area for module '\Example': 6.065280

If you are feeling brave and want to hack OpenROAD locally, these are the steps to do a local build:

git checkout origin/chisel-vs-handcoded

cd OpenROAD-flow-scripts

sudo ./setup.sh

./build_openroad.sh --local --openroad-args "-D CMAKE_BUILD_TYPE=RELEASE"

. setup_env.sh

cd flow

make DESIGN_CONFIG=designs/asap7/example/config.mk

Some direct links to source folders:

Epilogue: if I modify the Chisel to use "with RequireAsyncReset", I get

$ cat reports/asap7/example/base/synth_stat.txt

24. Printing statistics.

=== Example ===

Number of wires: 68

Number of wire bits: 68

Number of public wires: 8

Number of public wire bits: 8

Number of memories: 0

Number of memory bits: 0

Number of processes: 0

Number of cells: 60

AND2x2_ASAP7_75t_R 2

AND4x2_ASAP7_75t_R 1

AO21x1_ASAP7_75t_R 3

AO221x1_ASAP7_75t_R 1

AO31x2_ASAP7_75t_R 1

AO32x1_ASAP7_75t_R 2

BUFx2_ASAP7_75t_R 1

DFFASRHQNx1_ASAP7_75t_R 8

HAxp5_ASAP7_75t_R 4

INVx1_ASAP7_75t_R 12

NAND2x1_ASAP7_75t_R 5

NOR2x1_ASAP7_75t_R 1

NOR3x1_ASAP7_75t_R 1

OA211x2_ASAP7_75t_R 1

OA21x2_ASAP7_75t_R 3

OA31x2_ASAP7_75t_R 1

OA33x2_ASAP7_75t_R 2

OAI21x1_ASAP7_75t_R 1

OR3x1_ASAP7_75t_R 6

OR5x1_ASAP7_75t_R 1

TIEHIx1_ASAP7_75t_R 1

XNOR2x1_ASAP7_75t_R 1

XOR2x2_ASAP7_75t_R 1

Chip area for module '\Example': 8.077320

24. Printing statistics.

=== Example ===

Number of wires: 68

Number of wire bits: 68

Number of public wires: 8

Number of public wire bits: 8

Number of memories: 0

Number of memory bits: 0

Number of processes: 0

Number of cells: 60

AND2x2_ASAP7_75t_R 2

AND4x2_ASAP7_75t_R 1

AO21x1_ASAP7_75t_R 3

AO221x1_ASAP7_75t_R 1

AO31x2_ASAP7_75t_R 1

AO32x1_ASAP7_75t_R 2

BUFx2_ASAP7_75t_R 1

DFFASRHQNx1_ASAP7_75t_R 8

HAxp5_ASAP7_75t_R 4

INVx1_ASAP7_75t_R 12

NAND2x1_ASAP7_75t_R 5

NOR2x1_ASAP7_75t_R 1

NOR3x1_ASAP7_75t_R 1

OA211x2_ASAP7_75t_R 1

OA21x2_ASAP7_75t_R 3

OA31x2_ASAP7_75t_R 1

OA33x2_ASAP7_75t_R 2

OAI21x1_ASAP7_75t_R 1

OR3x1_ASAP7_75t_R 6

OR5x1_ASAP7_75t_R 1

TIEHIx1_ASAP7_75t_R 1

XNOR2x1_ASAP7_75t_R 1

XOR2x2_ASAP7_75t_R 1

Chip area for module '\Example': 8.077320

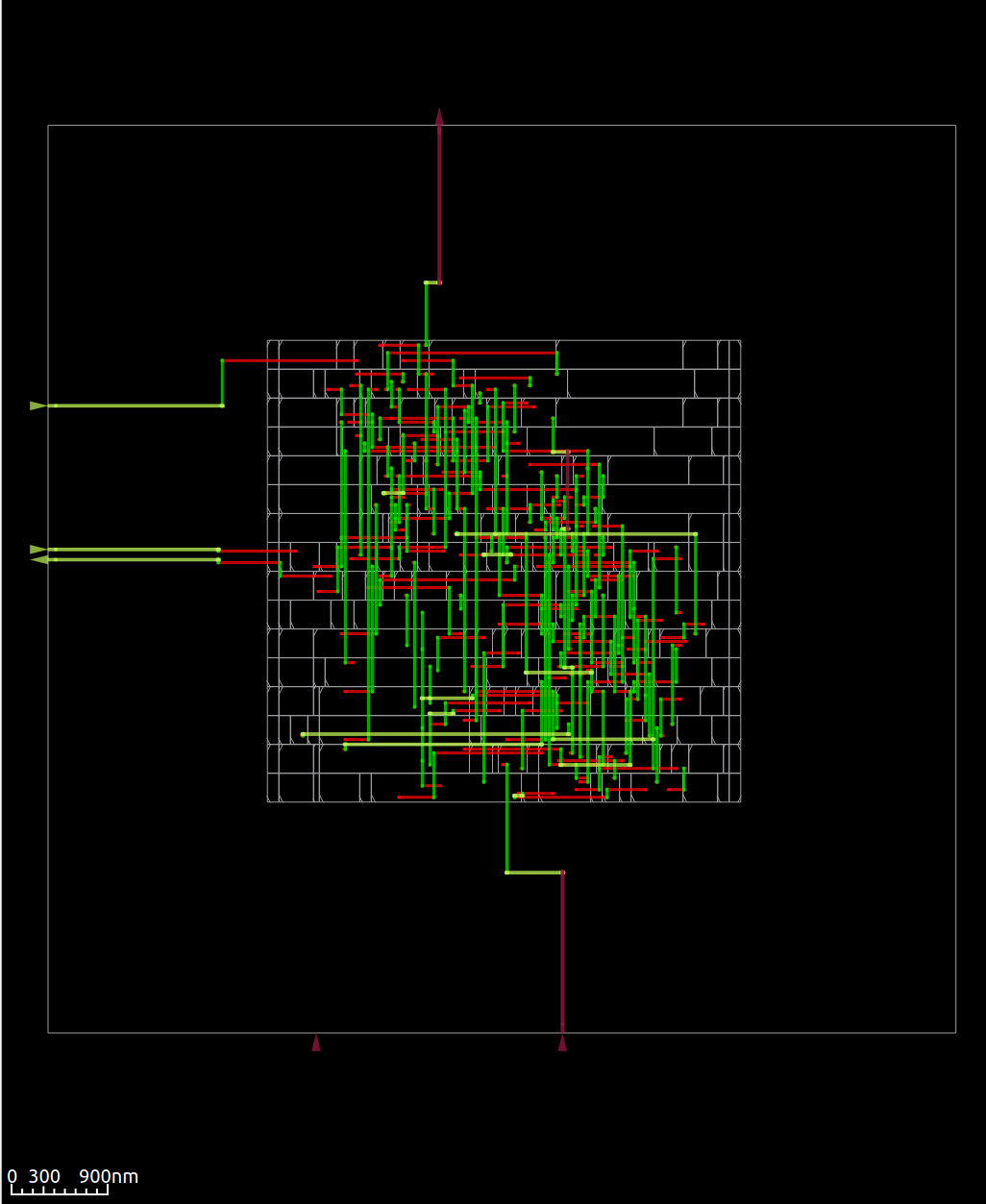

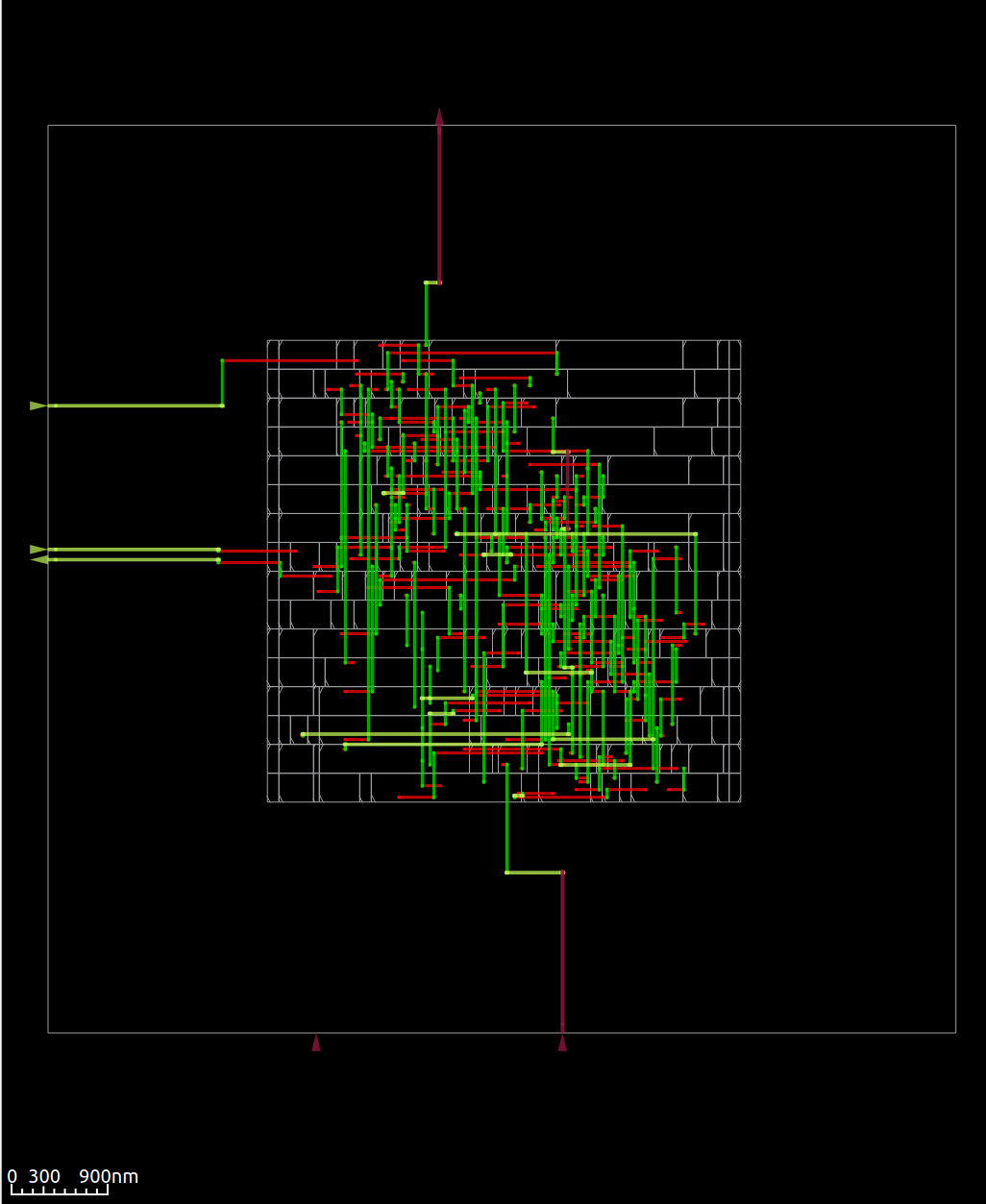

Epilogue #2 (make gui_final), clearly the floorplan needs tweaking in this case. Not sure that looking at for instance power & area for such a small example will make much sense...

Reply all

Reply to author

Forward

0 new messages