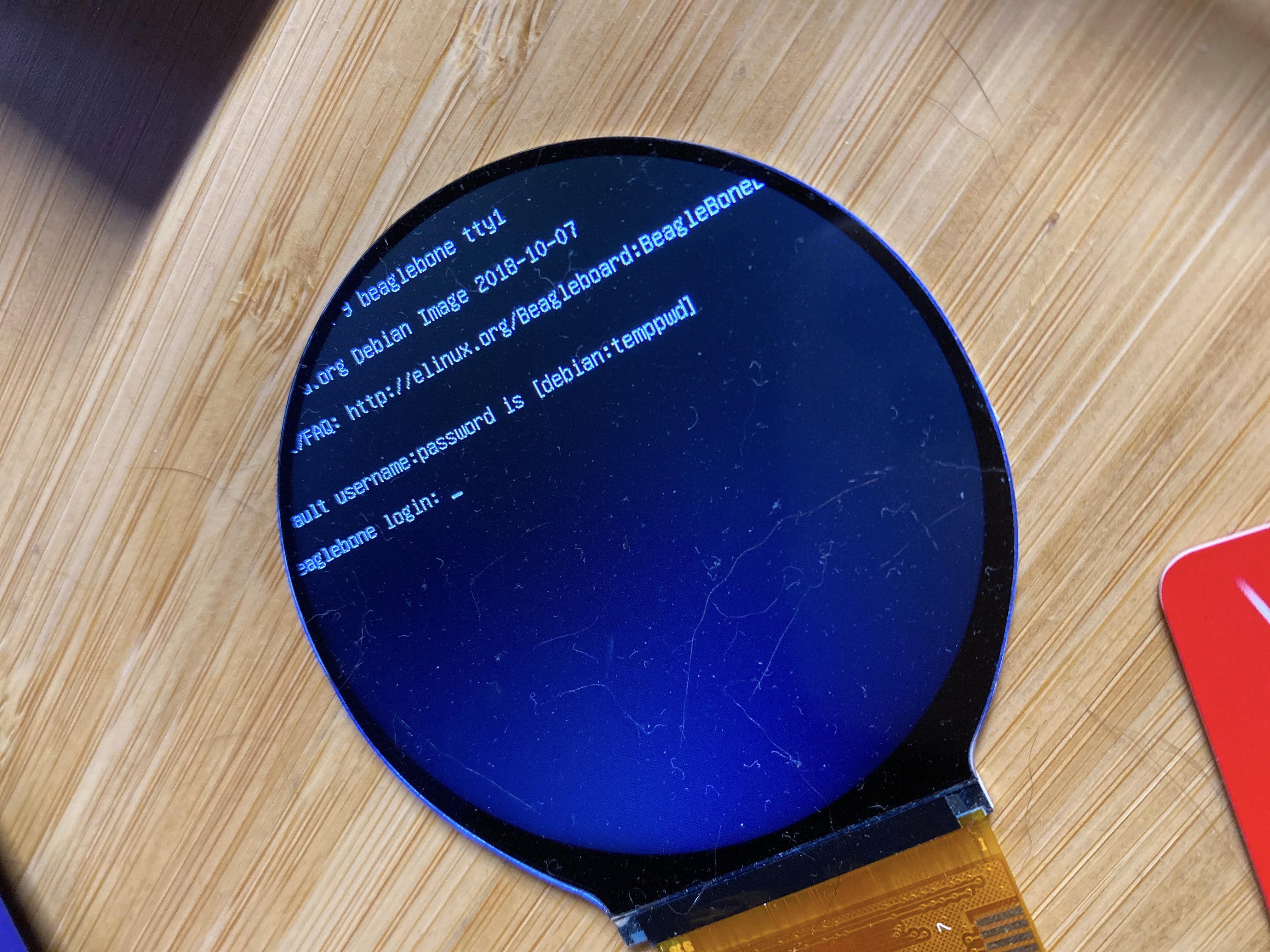

Garbled image on 16-bit parallel RGB LCD (Sitronix ST7701S)

Corey Vixie

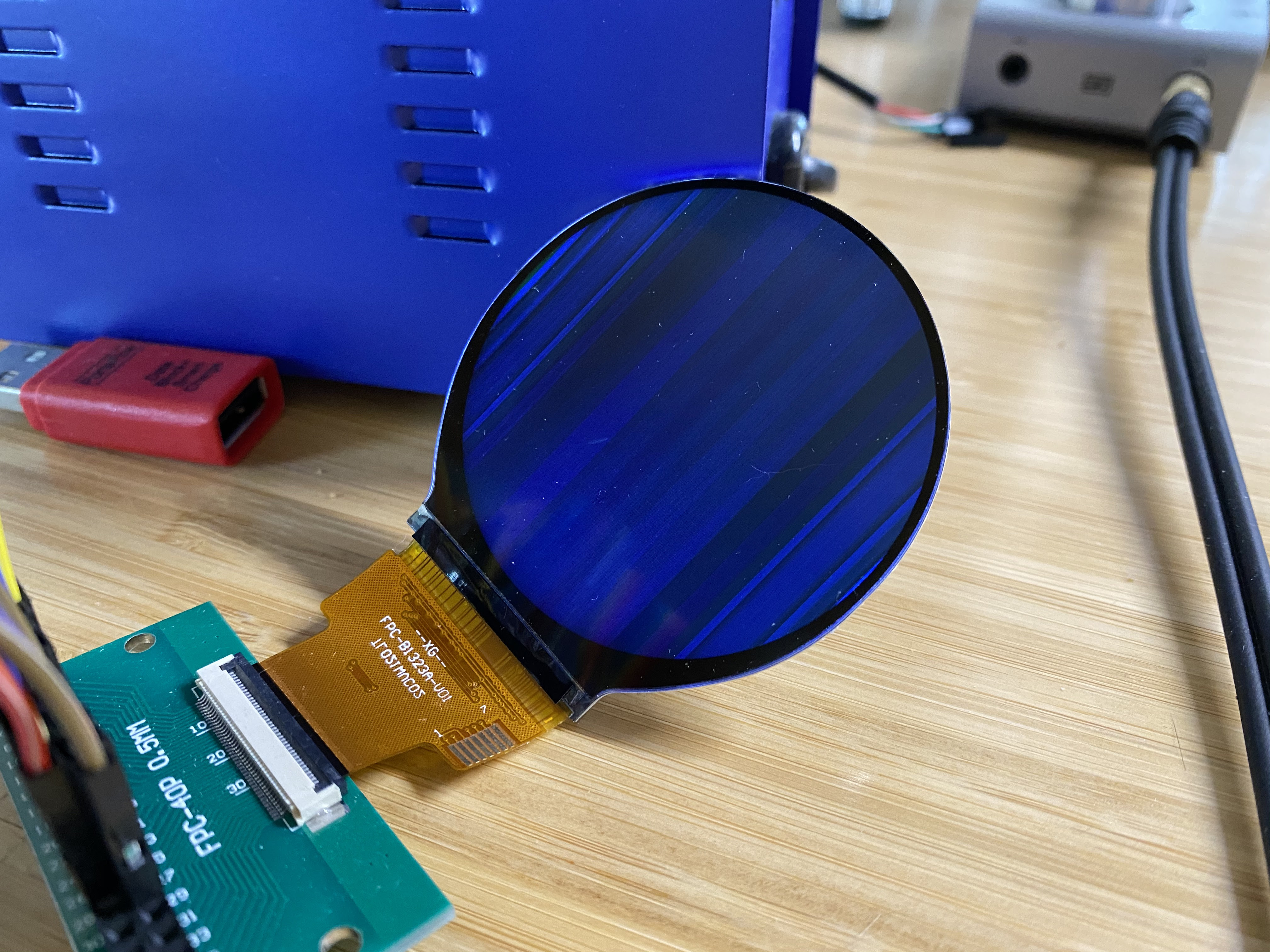

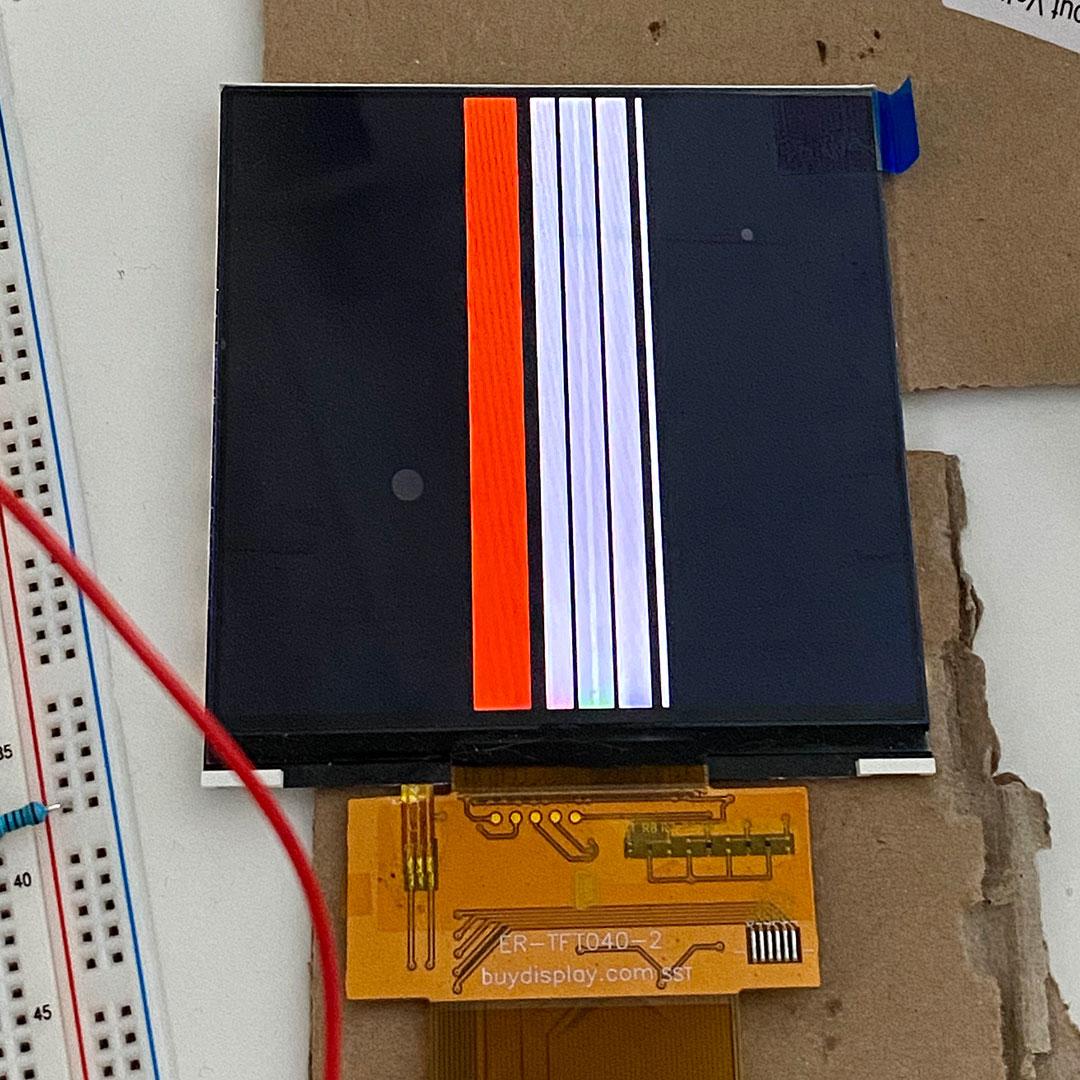

Using fim to render a pure white png produces this:

The OS is Debian Stretch 9.5 IoT from the Beaglebone website.

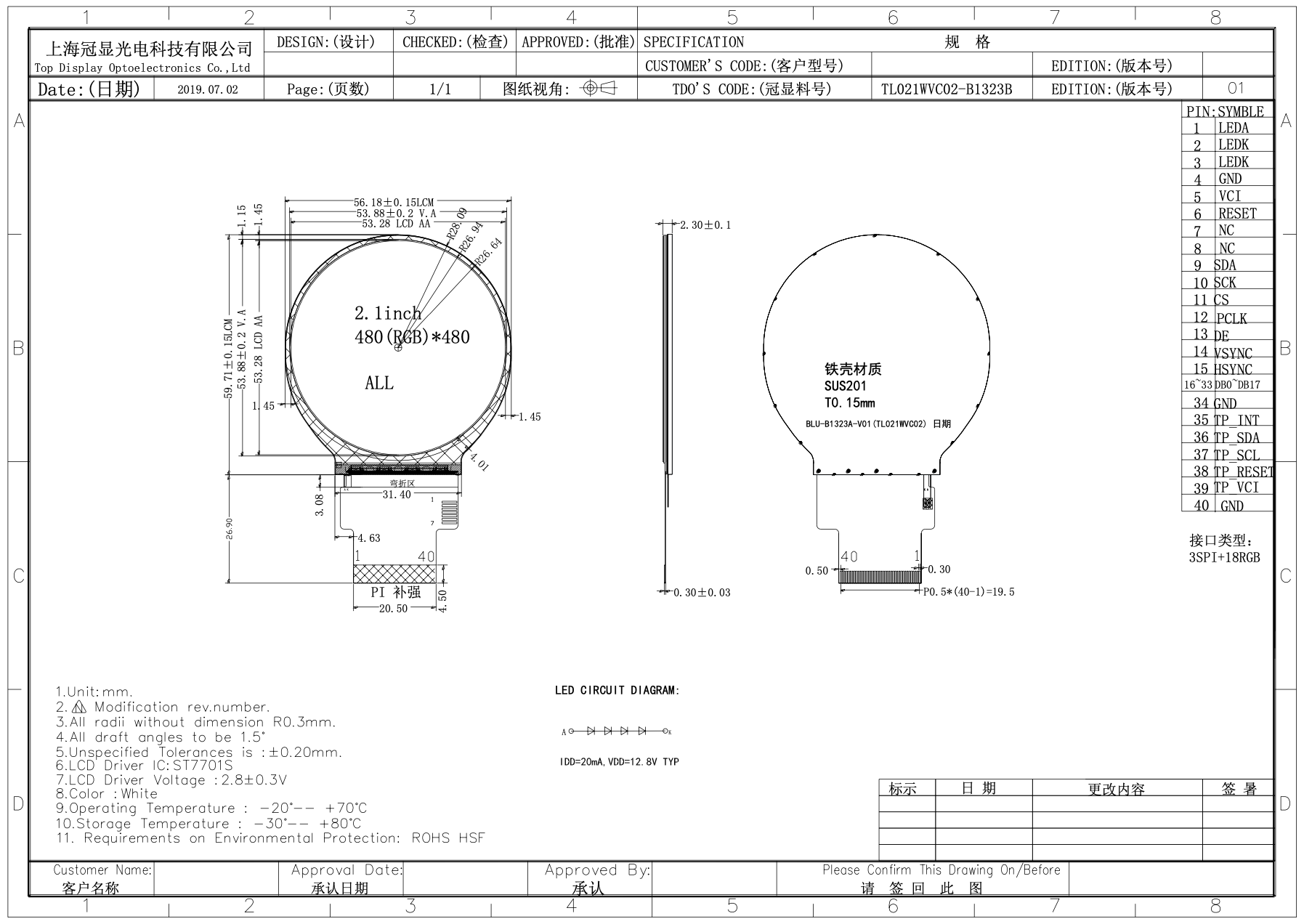

The display is connected as per the normal

The chosen resolution is 480x480@60Hz. I've also tried the CVT RB and CVT RBv2 variants of standard VGA (640x480@60Hz, which should be supported by the ST7701S), and the results are the same, just shifted on the display. All tested configurations are visible in the device tree overlay.

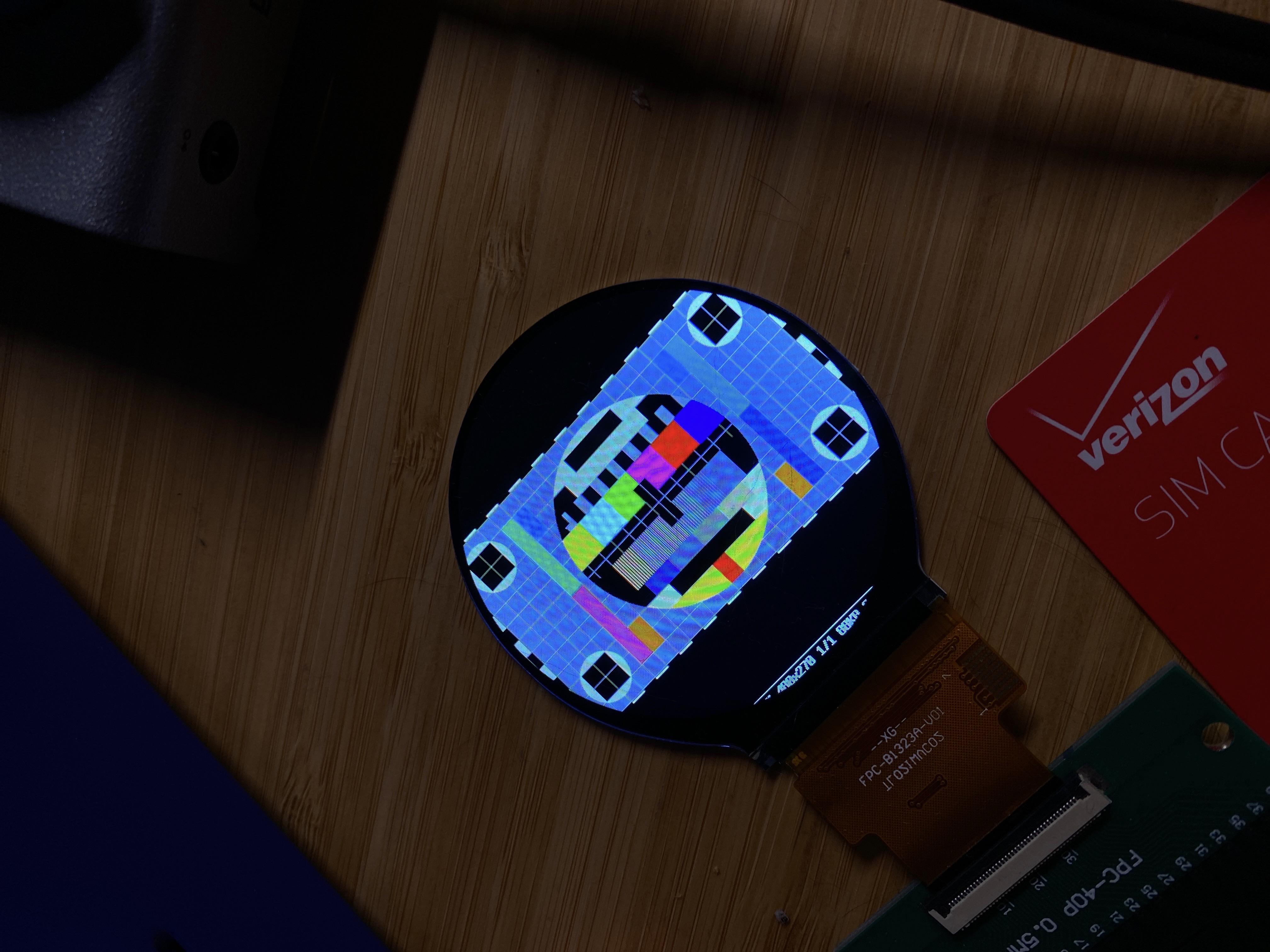

Using fim to display other test images produces similar results. My pure black png is dark, a color test pattern produces some green effects, etc.

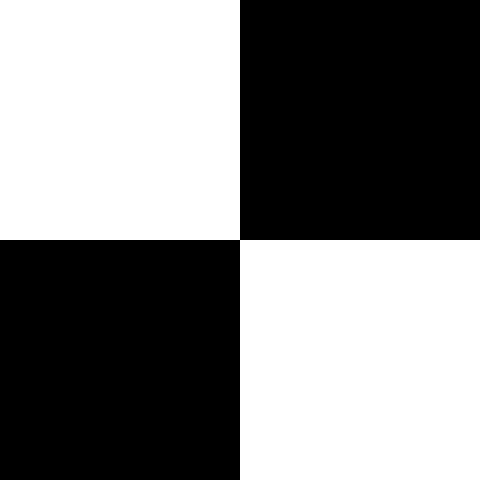

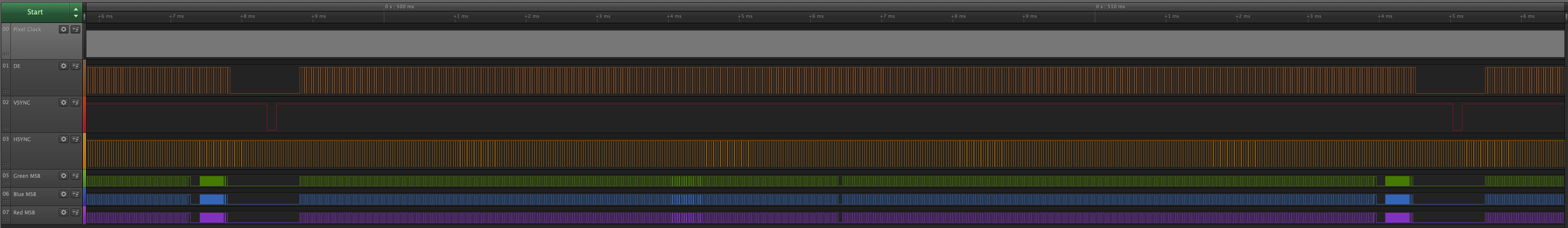

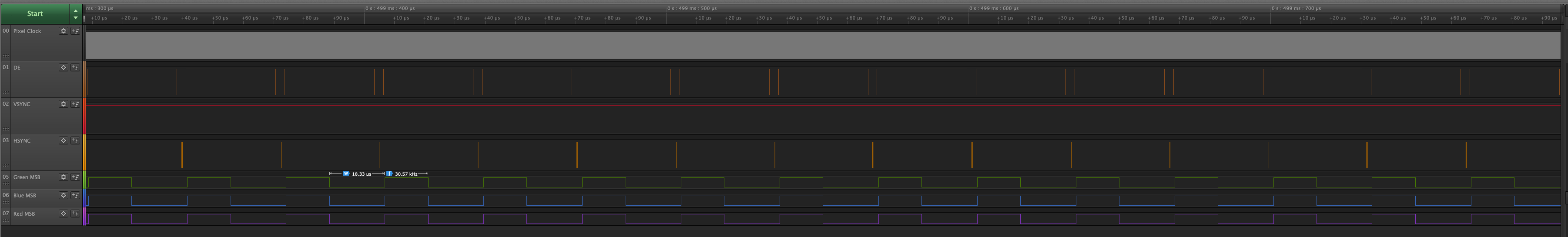

Testing the signal lines with a logic analyzer shows the expected values when sampling the MSB for each color. An excellent example is using a test image like this:

When zoomed to the level of a single frame, everything looks correct, like the datasheet. DE, VSYNC, and HSYNC polarity look good and correct. The VSYNC refresh rate tested at 59.97hz, which should be appropriate for the display.

When I zoom in to look at the timings for each line, everything also looks correct, and you can see the white and black pattern for each line in the MSB values. My logic analyzer can only sample as fast as 24MS/s, which does not accurately capture the pixel clock (which is was set to 16.15MHz for this test).

Relevant files:

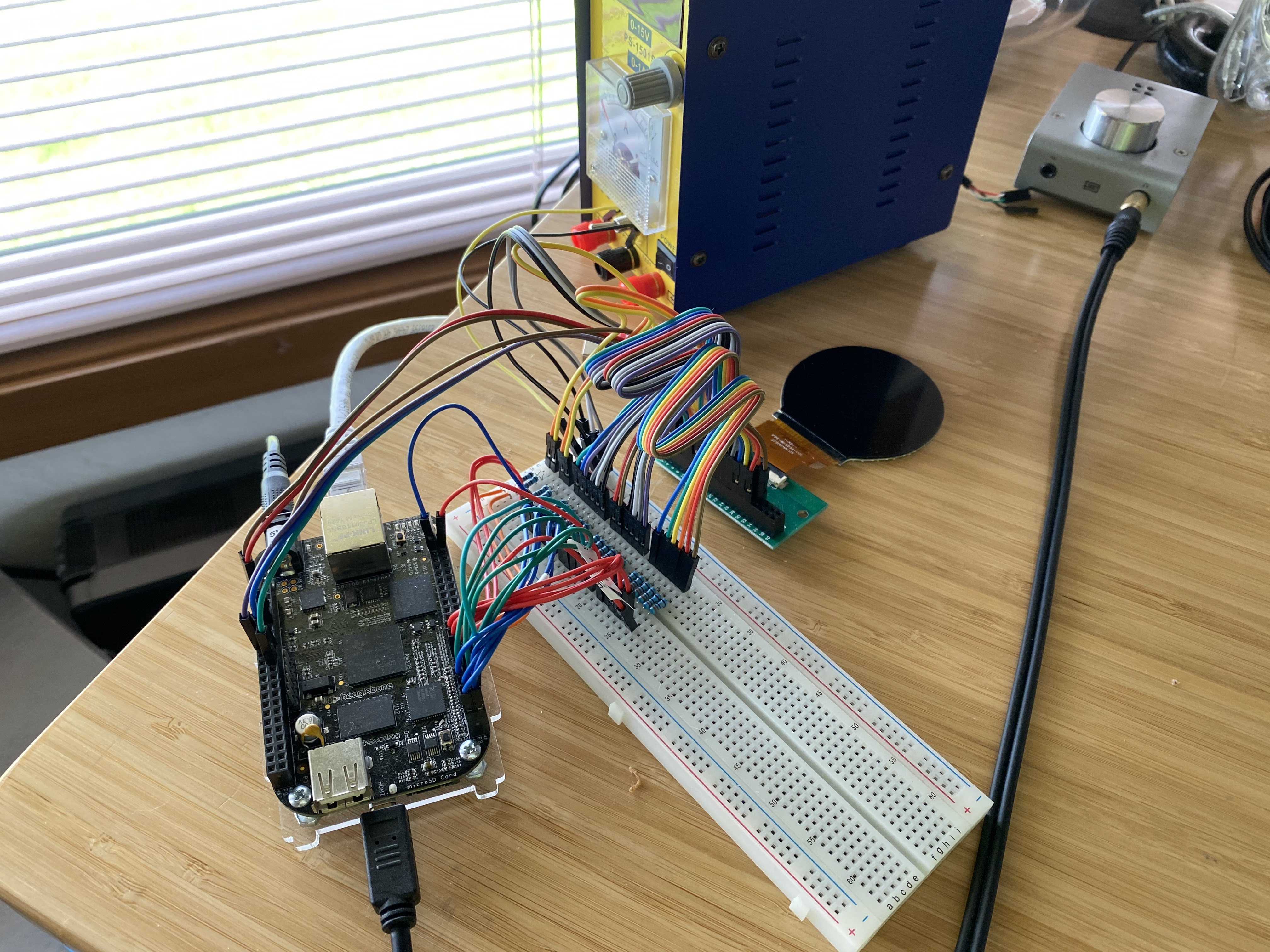

Here is the exact hardware setup I'm using:

| Function | Name | Pin | Resistor | Pin | Name |

|---|---|---|---|---|---|

| LED ANODE | +12.8v | DC PSU + | -- | 1 | LED A |

| LED CATHODE | GND | DC PSU - | -- | 2 | LED K |

| LED CATHODE | GND | DC PSU - | -- | 3 | LED K |

| Ground | DGND | P9.1 | -- | 4 | GND |

| Power supply | VDD 3.3V | P9.3 | -- | 5 | VCI |

| Reset Signal | GPIO_60 | P9.12 | -- | 6 | RESET |

| Not Connected | -- | -- | -- | 7 | NC |

| Not Connected | -- | -- | -- | 8 | NC |

| SPI Data signal | SPIO_D1 | P9.18 | -- | 9 | SDA |

| SPI Clock signal | SPIO_SLCK | P9.22 | -- | 10 | SCK |

| SPI Chip select signal | SPIO_CSO | P9.17 | -- | 11 | CS |

| RGB dot clock signal | LCD_PCLK | P8.28 | 33Ω | 12 | PCLK |

| RGB data enable signal | LCD_AC_BIAS | P8.30 | 33Ω | 13 | DE |

| RGB frame synchronizing signal | LCD_VSYNC | P8.27 | 33Ω | 14 | VSYNC |

| RGB line synchronizing signal | LCD_HSYNC | P8.29 | 33Ω | 15 | HSYNC |

| 📘B[0] | DGND | P8.1 | 33Ω | 16 | DB0 |

| 📘B[1] | LCD_DATA0 | P8.45 | 33Ω | 17 | DB1 |

| 📘B[2] | LCD_DATA1 | P8.46 | 33Ω | 18 | DB2 |

| 📘B[3] | LCD_DATA2 | P8.43 | 33Ω | 19 | DB3 |

| 📘B[4] | LCD_DATA3 | P8.44 | 33Ω | 20 | DB4 |

| 📘B[5] | LCD_DATA4 | P8.41 | 33Ω | 21 | DB5 |

| 📗G[0] | LCD_DATA5 | P8.42 | 33Ω | 22 | DB |

| 📗G[1] | LCD_DATA6 | P8.39 | 33Ω | 23 | DB |

| 📗G[2] | LCD_DATA7 | P8.40 | 33Ω | 24 | DB |

| 📗G[3] | LCD_DATA8 | P8.37 | 33Ω | 25 | DB |

| 📗G[4] | LCD_DATA9 | P8.38 | 33Ω | 26 | DB |

| 📗G[5] | LCD_DATA10 | P8.36 | 33Ω | 27 | DB |

| 📕R[0] | DGND | P8.2 | 33Ω | 28 | DB |

| 📕R[1] | LCD_DATA11 | P8.34 | 33Ω | 29 | DB |

| 📕R[2] | LCD_DATA12 | P8.35 | 33Ω | 30 | DB |

| 📕R[3] | LCD_DATA13 | P8.33 | 33Ω | 31 | DB |

| 📕R[4] | LCD_DATA14 | P8.31 | 33Ω | 32 | DB |

| 📕R[5] | LCD_DATA15 | P8.33 | 33Ω | 33 | DB |

Robert Forsyth

rap...@productionbuild.de

Robert Forsyth

On Monday, 30 March 2020 22:34:30 UTC+1, Corey Vixie wrote:

Robert Forsyth

rap...@productionbuild.de

What I was trying to say, if VS or HS change as the PCLK is rising, then it may not register, but the next PCLK clock should register the VS or HS

Corey Vixie

I always get the same effect as described by the OP: every line is looking the same. I've got full control over the x-axis, however, and can even run animations.

rap...@productionbuild.de

rap...@productionbuild.de

SPI_WriteComm (0x11);

delay(300);

SPI_WriteComm (0xFF);

SPI_WriteData (0x77);

SPI_WriteData (0x01);

SPI_WriteData (0x00);

SPI_WriteData (0x00);

SPI_WriteData (0x10);

SPI_WriteComm (0xC0);

SPI_WriteData (0x3B);

SPI_WriteData (0x00);

SPI_WriteComm (0xC1);

SPI_WriteData (0x0D);

SPI_WriteData (0x02);

SPI_WriteComm (0xC2);

SPI_WriteData (0x21);

SPI_WriteData (0x08);

SPI_WriteComm (0xB0);

SPI_WriteData (0x00);

SPI_WriteData (0x11);

SPI_WriteData (0x18);

SPI_WriteData (0x0E);

SPI_WriteData (0x11);

SPI_WriteData (0x06);

SPI_WriteData (0x07);

SPI_WriteData (0x08);

SPI_WriteData (0x07);

SPI_WriteData (0x22);

SPI_WriteData (0x04);

SPI_WriteData (0x12);

SPI_WriteData (0x0F);

SPI_WriteData (0xAA);

SPI_WriteData (0x31);

SPI_WriteData (0x18);

SPI_WriteComm (0xB1);

SPI_WriteData (0x00);

SPI_WriteData (0x11);

SPI_WriteData (0x19);

SPI_WriteData (0x0E);

SPI_WriteData (0x12);

SPI_WriteData (0x07);

SPI_WriteData (0x08);

SPI_WriteData (0x08);

SPI_WriteData (0x08);

SPI_WriteData (0x22);

SPI_WriteData (0x04);

SPI_WriteData (0x11);

SPI_WriteData (0x11);

SPI_WriteData (0xA9);

SPI_WriteData (0x32);

SPI_WriteData (0x18);

SPI_WriteComm (0xFF);

SPI_WriteData (0x77);

SPI_WriteData (0x01);

SPI_WriteData (0x00);

SPI_WriteData (0x00);

SPI_WriteData (0x11);

SPI_WriteComm (0xB0);

SPI_WriteData (0x60);

SPI_WriteComm (0xB1);

SPI_WriteData (0x30);

SPI_WriteComm (0xB2);

SPI_WriteData (0x87);

SPI_WriteComm (0xB3);

SPI_WriteData (0x80);

SPI_WriteComm (0xB5);

SPI_WriteData (0x49);

SPI_WriteComm (0xB7);

SPI_WriteData (0x85);

SPI_WriteComm (0xB8);

SPI_WriteData (0x21);

SPI_WriteComm (0xC1);

SPI_WriteData (0x78);

SPI_WriteComm (0xC2);

SPI_WriteData (0x78);

delay(20);

SPI_WriteComm (0xE0);

SPI_WriteData (0x00);

SPI_WriteData (0x1B);

SPI_WriteData (0x02);

SPI_WriteComm (0xE1);

SPI_WriteData (0x08);

SPI_WriteData (0xA0);

SPI_WriteData (0x00);

SPI_WriteData (0x00);

SPI_WriteData (0x07);

SPI_WriteData (0xA0);

SPI_WriteData (0x00);

SPI_WriteData (0x00);

SPI_WriteData (0x00);

SPI_WriteData (0x44);

SPI_WriteData (0x44);

SPI_WriteComm (0xE2);

SPI_WriteData (0x11);

SPI_WriteData (0x11);

SPI_WriteData (0x44);

SPI_WriteData (0x44);

SPI_WriteData (0xED);

SPI_WriteData (0xA0);

SPI_WriteData (0x00);

SPI_WriteData (0x00);

SPI_WriteData (0xEC);

SPI_WriteData (0xA0);

SPI_WriteData (0x00);

SPI_WriteData (0x00);

SPI_WriteComm (0xE3);

SPI_WriteData (0x00);

SPI_WriteData (0x00);

SPI_WriteData (0x11);

SPI_WriteData (0x11);

SPI_WriteComm (0xE4);

SPI_WriteData (0x44);

SPI_WriteData (0x44);

SPI_WriteComm (0xE5);

SPI_WriteData (0x0A);

SPI_WriteData (0xE9);

SPI_WriteData (0xD8);

SPI_WriteData (0xA0);

SPI_WriteData (0x0C);

SPI_WriteData (0xEB);

SPI_WriteData (0xD8);

SPI_WriteData (0xA0);

SPI_WriteData (0x0E);

SPI_WriteData (0xED);

SPI_WriteData (0xD8);

SPI_WriteData (0xA0);

SPI_WriteData (0x10);

SPI_WriteData (0xEF);

SPI_WriteData (0xD8);

SPI_WriteData (0xA0);

SPI_WriteComm (0xE6);

SPI_WriteData (0x00);

SPI_WriteData (0x00);

SPI_WriteData (0x11);

SPI_WriteData (0x11);

SPI_WriteComm (0xE7);

SPI_WriteData (0x44);

SPI_WriteData (0x44);

SPI_WriteComm (0xE8);

SPI_WriteData (0x09);

SPI_WriteData (0xE8);

SPI_WriteData (0xD8);

SPI_WriteData (0xA0);

SPI_WriteData (0x0B);

SPI_WriteData (0xEA);

SPI_WriteData (0xD8);

SPI_WriteData (0xA0);

SPI_WriteData (0x0D);

SPI_WriteData (0xEC);

SPI_WriteData (0xD8);

SPI_WriteData (0xA0);

SPI_WriteData (0x0F);

SPI_WriteData (0xEE);

SPI_WriteData (0xD8);

SPI_WriteData (0xA0);

SPI_WriteComm (0xEB);

SPI_WriteData (0x02);

SPI_WriteData (0x00);

SPI_WriteData (0xE4);

SPI_WriteData (0xE4);

SPI_WriteData (0x88);

SPI_WriteData (0x00);

SPI_WriteData (0x40);

SPI_WriteComm (0xEC);

SPI_WriteData (0x3C);

SPI_WriteData (0x00);

SPI_WriteComm (0xED);

SPI_WriteData (0xAB);

SPI_WriteData (0x89);

SPI_WriteData (0x76);

SPI_WriteData (0x54);

SPI_WriteData (0x02);

SPI_WriteData (0xFF);

SPI_WriteData (0xFF);

SPI_WriteData (0xFF);

SPI_WriteData (0xFF);

SPI_WriteData (0xFF);

SPI_WriteData (0xFF);

SPI_WriteData (0x20);

SPI_WriteData (0x45);

SPI_WriteData (0x67);

SPI_WriteData (0x98);

SPI_WriteData (0xBA);

SPI_WriteComm (0xFF);

SPI_WriteData (0x77);

SPI_WriteData (0x01);

SPI_WriteData (0x00);

SPI_WriteData (0x00);

SPI_WriteData (0x00);

SPI_WriteComm (0x29);Hao Yuin

H. Nikolaus Schaller

> Am 14.09.2020 um 10:23 schrieb Hao Yuin <hao...@gmail.com>:

>

> i have similar round LCD screen but still fail to bring it up. The Linux MIPI DSI driver will never work for the ST7701?? I tried modify panel-raydium-rm67191.c and add in these command sequence. No errors but still cannot get good image. Maybe my timing also out. May I know the timing (hfp, hbp, hsync, vfp, vbp, vsync) you are using?

There was a patch series posted a while ago by Sebastian Reichel to fix this but it is not yet reviewed and merged. So I would not expect it to arrive before v5.12 or v5.13...

For the meantime we have a MIPI-DSI panel running on omap5 (with v5.9):

https://git.goldelico.com/?p=letux-kernel.git;a=shortlog;h=refs/heads/letux/boe-w677-dsi-panel

We plan to move and update it for drm/panel which should not be too difficult but too early.

-- hns