H8 on a FPGA

Les Bird

Douglas Miller

"...and then installed into an H8 chassis" ... or in an Altoids tin...

I had thought about this to reproduce another pet-project of

mine, the Honeywell 200/2000 mainframe computer. But for that

there is very little detail on the hardware implementation. In

that case, I would have wanted it to be a true implementation of

the original hardware, to answer questions about how the CPU

actually worked.

Last time I worked with FPGAs, 20 years ago, they had to be programmed via JTAG. These days I think it's easier, and I believe they even have non-volatile programming now. There are tools for converting things like VHDL (hardware description language) into FPGA programs, which is probably the best way to implement it (analogous to having source code and compiling it). There may be VHDL available for some of the ICs as well, although it may be easier to simply write (most of) the H8 "simulation" as VHDL.

Cool idea, but I have no clue about the practicality of it. I've

always wanted to get into making my own FPGAs.

--

You received this message because you are subscribed to the Google Groups "SEBHC" group.

To unsubscribe from this group and stop receiving emails from it, send an email to sebhc+un...@googlegroups.com.

To view this discussion on the web visit https://groups.google.com/d/msgid/sebhc/aab8de6c-ac20-4b15-8a49-3a203651b87bn%40googlegroups.com.

Mark Garlanger

To view this discussion on the web visit https://groups.google.com/d/msgid/sebhc/1dedf5ef-4aea-fcbc-33c9-7d1915169695%40gmail.com.

Les Bird

Les Bird

PRL-89

Dave McGuire

> Me, I’m finishing up the design for building an “almost” Z80 on

> breadboards using discrete components.

Either way I'd love to see pics and more info.

> Yes, I know. Insane.

I would say "wonderful", but that's just me.

-Dave

--

Dave McGuire, AK4HZ

New Kensington, PA

Les Bird

PRL-89

Thanks Dave!

PRL-89

Dave McGuire

This sounds absolutely fantastic. If you distill this down to a PCB

layout (or several), I'd definitely put one together.

-Dave

> You received this message because you are subscribed to the Google

> Groups "SEBHC" group.

> To unsubscribe from this group and stop receiving emails from it, send

> an email to sebhc+un...@googlegroups.com

> <https://groups.google.com/d/msgid/sebhc/88e4f3be-cee3-4828-9fdf-b55cdeac3f74n%40googlegroups.com?utm_medium=email&utm_source=footer>.

Rob Doyle

If you want to learn about FPGA, this is an excellent way to start.

The Terasic DE10-Nano (FPGA board used by MiSTer) will easily support an

H8 design including all of the goodies. Probably 10 of them or more.

I've used the DE10-Nano to build a Digital Equipment Corp KS10 36-bit

mainframe-ish computer with all the peripherals. The CPU is implemented

close-enough to the original to execute the original DEC microcode. I do

have an external 4 MB Synchronous SRAM (1 MW x 36) but everything else

is on-chip. This includes a disk controller for 8 washing machine sized

disk drives (storage is an SD Card), a tape controller for 8 tape

drives, a terminal multiplexer for 8 terminals, a communications

co-processor, high-speed synchronous communications adapter, printer, etc.

I've generated about 33,000 lines of verilog code and I still have used

only 29 percent of the logic cells and 9 percent of the on-chip memory.

The CPU and peripherals pass most of the DEC diagnostics.

https://github.com/KS10FPGA/KS10FPGA/wiki

If you need help or get stuck, help is probably lurking nearby.

Rob.

> You received this message because you are subscribed to the Google

> Groups "SEBHC" group.

> To unsubscribe from this group and stop receiving emails from it, send

> an email to sebhc+un...@googlegroups.com

> <mailto:sebhc+un...@googlegroups.com>.

> To view this discussion on the web visit

> <https://groups.google.com/d/msgid/sebhc/aab8de6c-ac20-4b15-8a49-3a203651b87bn%40googlegroups.com?utm_medium=email&utm_source=footer>.

Les Bird

Rob Doyle

It is my opinion that if you can draw schematics using 74xx chips - that

is the hard part.

Writing verilog is mostly just learning how to code a D flip-flop,

multiplexers, decoders, counters, shift registers, and combinational

logic. Once that is understood, you get an occasional FIFO, memory,

adder, or state machine.

Perhaps the most complicated thing is learning how the tools work. I

tend to script everything (unix makefiles) so I don't have to push

buttons on a GUI. With a single command, I can rebuild the firmware and

load it into the FPGA.

The verilog simulators work very well. I have a testbench wrapped

around the KS10 that provides simulated peripherals. For example, I

mentioned that the disk controller stores data on a SD Card. The

testbench has a simulation model for the SD Card that stores data on the

PC. The testbench also simulates memory and has a partial model for

RS-232 terminal. I can boot the CPU, the disk controller interacts with

the SD Card simulation and can read executables from my PC, I can watch

the CPU execute instructions, see RS-232 IO on a window, and can look at

any signal in the FPGA on something that looks like a 10,000 channel

logic analyzer.

Debugging on target hardware can be a little complicated. I added

breakpoint hardware into the CPU. It can stop the CPU on instruction

fetches, memory reads, memory writes, IO reads, and IO writes to an

address. I can read or write the internal registers. It also has an

instruction trace buffer which records the program counter in a large

FIFO - for traceback - which answers the age-old question: How did I get

here? These are all things that a Z80 could never do...

Rob.

> <https://groups.google.com/d/msgid/sebhc/aab8de6c-ac20-4b15-8a49-3a203651b87bn%40googlegroups.com?utm_medium=email&utm_source=footer>>.

>

> --

> You received this message because you are subscribed to the Google

> Groups "SEBHC" group.

> To unsubscribe from this group and stop receiving emails from it, send

> an email to sebhc+un...@googlegroups.com

> <mailto:sebhc+un...@googlegroups.com>.

> To view this discussion on the web visit

> <https://groups.google.com/d/msgid/sebhc/e5c678de-7d3f-4657-9993-b60ff8e960b0n%40googlegroups.com?utm_medium=email&utm_source=footer>.

Norberto Collado

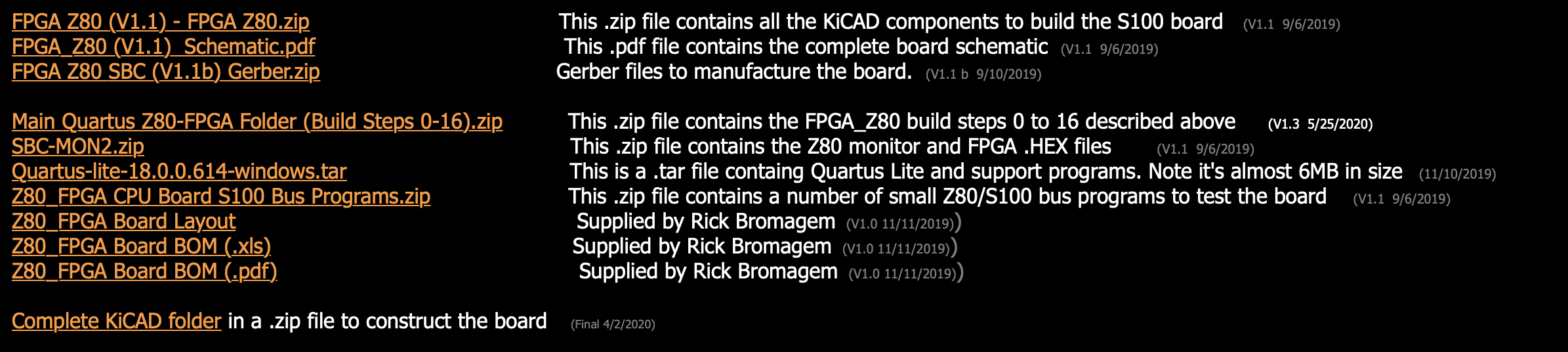

There is an article with introductions to FPGA that uses the Altera FPGA to create a Z80 that can be run at 50MHz. Perhaps something can be leverage to make this easier as it provides everything.

http://www.s100computers.com/My%20System%20Pages/FPGA%20Z80%20SBC/FPGA%20Z80%20SBC.htm

Norberto

To unsubscribe from this group and stop receiving emails from it, send an email to sebhc+un...@googlegroups.com.

To view this discussion on the web visit https://groups.google.com/d/msgid/sebhc/71ef4e94-184d-87d6-2fbe-9e359edc0eb4%40gmail.com.

George Farris

To view this discussion on the web visit https://groups.google.com/d/msgid/sebhc/6F05EE5C-7E4F-4AB0-9BE4-2BE2258FEBD2%40koyado.com.