New Z67-SD Controller

Norberto Collado

Terry Smedley

Glenn Roberts

Terry: when you boot using “universal” sequence can you tell if the Z67-IDE+ consistently reads the software boot code record (LED shows brief disk activity)? If not then the problem might be with PAM 37?; if yes then we could look at the software boot code. I disassembled and commented this a while back. Norberto has the listing on his site

http://koyado.com/Heathkit/HDOS_H67_Boot_Code_files/bootcf0b%20Listing.pdf

this is the first code loaded off the Z67 and it is what presents the boot image selection menu.

Since you have gotten this to run at least occasionally we know that at least those times the Z67 read worked.

Don’t know if you can spot anything in this code that would be an issue. Or could compare to the boot code in BOOT and/or the H37 boot to see what those do that this doesn’t?

Do we know that the PAM-37 is fully compatible with the board? Trionyx apparently sold their own firmware (below).

I also saw that the Trionyx board implements “software control of all three Z80 interrupt modes” (which the Heath and DG boards do not do). Could it be that the interrupt processing is somehow not being initialized properly (since you’re observing inconsistent failures)?

--

You received this message because you are subscribed to the Google Groups "SEBHC" group.

To unsubscribe from this group and stop receiving emails from it, send an email to sebhc+un...@googlegroups.com.

To view this discussion on the web visit https://groups.google.com/d/msgid/sebhc/af63f091-4ed9-4313-b632-c1228ff46fa5n%40googlegroups.com.

Terry Smedley

You received this message because you are subscribed to a topic in the Google Groups "SEBHC" group.

To unsubscribe from this topic, visit https://groups.google.com/d/topic/sebhc/rYvPGsJBy8w/unsubscribe.

To unsubscribe from this group and all its topics, send an email to sebhc+un...@googlegroups.com.

To view this discussion on the web visit https://groups.google.com/d/msgid/sebhc/025001d6be20%24ae6369f0%240b2a3dd0%24%40gmail.com.

Glenn Roberts

You could also try replacing the Heathkit boot process with the Quickstor one which uses a different boot code. Ken Owen can probably help with any questions. He has a lot of info on Norberto’s site though, including some images that you can burn directly to a CF card…

http://koyado.com/Heathkit/Z67-IDE-plus.html

there’s a lot of stuff there and not that well organized but Ken or Norberto can probably help you figure it out.

To view this discussion on the web visit https://groups.google.com/d/msgid/sebhc/CALt%2BXpM_zgirvz_%3DSZ-HN-Wf4Rh-_a5GCviVX4o750Tr56corw%40mail.gmail.com.

terry.smedley

Kenneth L. Owen

Hi Terry,

I have teamed with Norberto to try to give implementation support to the group members who are trying to implement the Z67-IDE and Z67-IDE+ on their Heaths.

I have increasingly been less active on the group over the past 10 years as my wife was not well, declining in health and needed me more that the group! She passed away in August of this year and I am trying to get back into things that had to fall by the wayside over the past 10 years.

Feel free to contact me directly for your needs. It may take me a bit to get back up to speed on things, but I will give you my best. My email addy is: tx83...@bellsouth.net

- ken

Sent from Mail for Windows 10

To view this discussion on the web visit https://groups.google.com/d/msgid/sebhc/5fb69c06.1c69fb81.f9ffd.07aa%40mx.google.com.

Norberto Collado

Please try the following image and use the Windows tool to deploy it on CF#0.

Image: http://koyado.com/Heathkit/Z67-IDE-plus_files/H37_H67_Heath_HDOS_CPM_Drive0.zip

Tool: http://koyado.com/Heathkit/Z67-IDE-plus_files/Z67-IDE%20Windows%20Imaging%20Utility.zip

If booting from this image fails, then you have a corrupted PAM-37 monitor or a marginal broken CPU.

Make sure all the switches on the H67 are set to the “ON” position (DS1), to the right of the arrow on the switch.

Thanks,

Norberto

To view this discussion on the web visit https://groups.google.com/d/msgid/sebhc/004a01d6be7b%2492590250%24b70b06f0%24%40gmail.com.

Norberto Collado

Also I developed the Z67-IDE+ on the Trionyx CPU using the PAM-37 monitor.

Norby

To view this discussion on the web visit https://groups.google.com/d/msgid/sebhc/CC959DD5-287D-4CE8-9A03-9F7A4B8E6E3C%40koyado.com.

Steven Hirsch

> I have increasingly been less active on the group over the past 10 years as

> my wife was not well, declining in health and needed me more that the

> group! She passed away in August of this year and I am trying to get back

> into things that had to fall by the wayside over the past 10 years.

I'm so sorry to hear about your wife. My condolences and best wishes go out

to you!

Steve

Terry Smedley

Terry Smedley

Glenn Roberts

It seems like Trionyx did this a lot. I had a few of their memory boards and there were multiple patches applied over time. The temptation is to remove them but they were all bug fixes or enhancements, if you can track down the documentation…

To view this discussion on the web visit https://groups.google.com/d/msgid/sebhc/98ad6326-2f64-4bf4-af85-4bc2058f466an%40googlegroups.com.

Terry Smedley

Norberto Collado

To view this discussion on the web visit https://groups.google.com/d/msgid/sebhc/63efee63-dfe1-4d0e-a8c5-68223da04000n%40googlegroups.com.

Terry Smedley

Terry Smedley

Terry Smedley

Norberto Collado

If you leave the system hung for at least 5 minutes, do you get any other information? Just curious.

If not, send me the Z67-IDE+ to check it out.

Address: Norberto, Collado, P. O. Box 988 Hillsboro, OR 97123-0988

Thanks,

Norberto

To view this discussion on the web visit https://groups.google.com/d/msgid/sebhc/dcaafb32-83aa-4836-899d-14a06dc00e13n%40googlegroups.com.

Norberto Collado

Yes, type the “esc” command to enter the menu.

Norberto

To view this discussion on the web visit https://groups.google.com/d/msgid/sebhc/308a8a61-728e-4a70-9bbe-6893ae21a588n%40googlegroups.com.

Norberto Collado

Any updates???

Terry Smedley

Norberto Collado

Thanks for the update! Please check your serial board to be configured properly. Also check your RS-232 handshaking signals as well. It seems to be stuck polling the serial port based on your description, but not sure. Have you seen on the Z67-IDE+ any watchdog timeout messages?

When you use the PAM-37+ image I gave you, do you see on the screen “H8 Initialized…” on power-on?

I will review your data tomorrow again. I can send you a modify FW for the microcontroller that will display the command and data read/written.

Thanks,

Norberto

Any updates???

Error! Filename not specified.

To view this discussion on the web visit https://groups.google.com/d/msgid/sebhc/a43b13dc-9412-4803-8449-350bf688c868n%40googlegroups.com.

Terry Smedley

Glenn Roberts

To view this discussion on the web visit https://groups.google.com/d/msgid/sebhc/7139eba7-6b55-4869-abe8-ef62ccf55c36n%40googlegroups.com.

Glenn Roberts

Terry Smedley

To view this discussion on the web visit https://groups.google.com/d/msgid/sebhc/CACkv5mDvBgyOLL2ONR6pMuKO0KLY0zPT%3DUHV_gTeEO8Nfn1E7A%40mail.gmail.com.

Glenn Roberts

To view this discussion on the web visit https://groups.google.com/d/msgid/sebhc/CALt%2BXpNns36J1%3D7UN8P18Qqi7fpPm4%3D8f%3DnvzMNVzep%2B-2V%2BhA%40mail.gmail.com.

Kenneth L. Owen

Hi Terry,

I have been out of the loop for quite a while due to caring for my wife. Since I don’t remember the image file below, I can’t give you very specific instruction, you might want to pull the Z67 card and set all switches on. This will give you the SASIX boot menu if that image is using it. Also, you can try the command line: “Boot SS-0 <cr> If the image is using the SASIX Boot system it should boot partition 0 of the system.

To view this discussion on the web visit https://groups.google.com/d/msgid/sebhc/CALt%2BXpNns36J1%3D7UN8P18Qqi7fpPm4%3D8f%3DnvzMNVzep%2B-2V%2BhA%40mail.gmail.com.

Terry Smedley

To view this discussion on the web visit https://groups.google.com/d/msgid/sebhc/CACkv5mCEoWOAE2vqDP1K73CNuAFQv%3Dx6N2KZBs3tuQAqv-GsDA%40mail.gmail.com.

Norberto Collado

If HDOS QuikStor works fine, then you were using the wrong port #. Great news.

Norberto

To view this discussion on the web visit https://groups.google.com/d/msgid/sebhc/CALt%2BXpO_XWpUXhvaoSV2-sh6910CxRyrQ-hAjh3b80ckEtyZPA%40mail.gmail.com.

Terry Smedley

To view this discussion on the web visit https://groups.google.com/d/msgid/sebhc/3481B136-0193-4FA0-BE39-1CD3E86EA84A%40koyado.com.

Kenneth L. Owen

Hi Terry,

The SASIX boot screen needs the H-19 Terminal using VT-52 mode and the Heath enhancements. If you don’t have an H-19 Terminal, several on the group have H-19 emulators that they have developed. I believe George Farris has one that will work with the SASIX boot system. Contact him here in the group.

- Ken

To view this discussion on the web visit https://groups.google.com/d/msgid/sebhc/CALt%2BXpO_XWpUXhvaoSV2-sh6910CxRyrQ-hAjh3b80ckEtyZPA%40mail.gmail.com.

Terry Smedley

To view this discussion on the web visit https://groups.google.com/d/msgid/sebhc/5fb9c933.1c69fb81.5895a.7a12SMTPIN_ADDED_MISSING%40gmr-mx.google.com.

Norberto Collado

Glenn Roberts

On Nov 24, 2020, at 4:06 AM, Norberto Collado <norberto...@koyado.com> wrote:

--

You received this message because you are subscribed to the Google Groups "SEBHC" group.

To unsubscribe from this group and stop receiving emails from it, send an email to sebhc+un...@googlegroups.com.

To view this discussion on the web visit https://groups.google.com/d/msgid/sebhc/20201124020545.1321cca37f09b4ab87c5049afdc8ceaa.11994675f8.wbe%40email09.godaddy.com.

<New_Z67_board.pdf><H8-Z67-SD CONTROLLER.JPG>

Douglas Miller

Had a thought, and keep in mind I know nothing about this

microcontroller and it's SDK. But, does the SDCard library support

a partition table (e.g. MS-DOS boot sector (MBR), or more modern

forms) on the SDCard? And if so, do we want to use it? This would,

in theory, allow one to partition the huge SDCard into

"reasonably" sized partitions for HDOS or CP/M on the host, and no

longer be constrained by the 128M fixed segment size. It makes it

easier to update and backup images on the card from the host PC,

and provides the potential for less wasted space. Still, it's a

trade-off and I'm not sure if it is worth it.

And, of course, Glenn's comment about making sure one can

insert/remove the cards without disassembling the unit would be

essential.

--

Norberto Collado

For accessing SD cards from the front, the only solution I know is to use an extension which sells at Amazon.

If someone knows a better solution, please let us know.

Thanks,

Norberto

From: "se...@googlegroups.com" <se...@googlegroups.com> on behalf of Glenn Roberts <glenn.f...@gmail.com>

Reply-To: "se...@googlegroups.com" <se...@googlegroups.com>

Date: Tuesday, November 24, 2020 at 2:46 AM

To: "se...@googlegroups.com" <se...@googlegroups.com>

To view this discussion on the web visit https://groups.google.com/d/msgid/sebhc/6C1F5BDB-F46D-4BC0-99B1-3F61A3E30AA0%40gmail.com.

Norberto Collado

The 128MB limit is because of CP/M supporting 8MB * 15 partitions + spares MB. HDOS uses 15MB if using Glenn changes. This allows me to divide a 4GB CF card into 128MB chunk sizes. What is a reasonably sized partition?

I know that the SCSI2IDE controller was tested with a Z80 using the SDCard MSDOS library and performance was very poor. With CF cards was much better.

https://www.retrobrewcomputers.org/doku.php?id=boards:other:scsi2ide:start

Thanks,

Norberto

From: "se...@googlegroups.com" <se...@googlegroups.com> on behalf of Douglas Miller <durga...@gmail.com>

Reply-To: "se...@googlegroups.com" <se...@googlegroups.com>

Date: Tuesday, November 24, 2020 at 4:20 AM

To: "se...@googlegroups.com" <se...@googlegroups.com>

Subject: Re: [sebhc] New Z67-SD Controller

Had a thought, and keep in mind I know nothing about this microcontroller and it's SDK. But, does the SDCard library support a partition table (e.g. MS-DOS boot sector (MBR), or more modern forms) on the SDCard? And if so, do we want to use it? This would, in theory, allow one to partition the huge SDCard into "reasonably" sized partitions for HDOS or CP/M on the host, and no longer be constrained by the 128M fixed segment size. It makes it easier to update and backup images on the card from the host PC, and provides the potential for less wasted space. Still, it's a trade-off and I'm not sure if it is worth it.

To view this discussion on the web visit https://groups.google.com/d/msgid/sebhc/361d028c-7e6e-b375-6069-da9d6490d6d9%40gmail.com.

Norberto Collado

Glenn,

I saw this board which shows that I need to extend the SD adapter out of the board to be access from the front. I will incorporate such change as we can do a 3D print case for it. See attached picture.

Norberto

To view this discussion on the web visit https://groups.google.com/d/msgid/sebhc/210A260B-2E35-4B17-96A4-061727F15918%40koyado.com.

Douglas Miller

It may be better to just access the SDCard "raw", but I thought I'd ask. FYI, CP/M 3 does not have the 8M partition limitation, it can support a 256M drive (partition). It just seemed that getting out of the fixed-size segment might be worth exploring.

I'm not sure why the performance would be worse, seems to me that

the partition table should be read only once at power-up of the

Z67-IDE (or Z67-SDC as the case may be) - or rather at insertion

of the SDCard if supporting hotplug, so I don't think the Z80

comes into it at all. Keep in mind, I'm suggesting that the

microcontroller in the Z67-SDC use the MBR partition table, not

the Z80 (CP/M). I was thinking that each MS-DOS partition on the

SDCard be "exported" by the Z67-SDC as a raw disk, and CP/M /

QuickStore / HDOS, whatever might sub-partition it as needed. So,

instead of the fixed-size 128M "segments", the Z67-SDC just reads

the MBR partition information and uses those partitions instead of

the fixed segments. But, if the SDK you are using does not have

library support for MBR, it wouldn't make sense. And if the

microcontroller is limited in speed and/or memory, it also may not

make sense.

To view this discussion on the web visit https://groups.google.com/d/msgid/sebhc/49F135BD-6A87-409B-BCEE-61E4DCED1514%40koyado.com.

Glenn Roberts

That’s exactly what I was thinking. Thanks!

To view this discussion on the web visit https://groups.google.com/d/msgid/sebhc/C0BD9CCD-2CC3-4586-8D72-EF956C817B71%40koyado.com.

Norberto Collado

The current Z67-IDE+ supports only the 128MB when using the switches to divide the CF card. If you leave the switches at “00”, then all 1GB range is available to the system. Today 256MB partitions are supported, but the user must avoid selecting such partition with the switches. So for 256MB, the user will select “00” and the next available partition will be “002” as “00”-> “01” will be used by CP/M3 OS. For this controller, I will use the 256MB range to divide the SD card as it makes sense to redo some of the Heath CP/M-HDOS images.

Please send me a CP/M3 256MB image to test with the current Z67-IDE controller. I want to see it any issues.

I will review about the MBR to understand on how that works. Yes, we need to use raw as it is a 20MHz 8bit CPU with 1KB of RAM. It is faster than the original SASI 10MB hard drive.

Thanks for the feedback,

To view this discussion on the web visit https://groups.google.com/d/msgid/sebhc/42dcf794-bdbb-0174-ad0d-a732775accbd%40gmail.com.

Douglas Miller

I was not aware that the Z67-IDE+ did not enforce the end of the segment. So, it is possible to corrupt later segments on a CF card?

I mis-quoted earlier, CP/M 3 supports drives of up to 512M each.

The MMS "master boot record" supports 8 (or maybe 9) partitions, so for CP/M 3 one could use 4+G of space on the card. I'll need to make sure my Z67-IDE+ emulation supports the above behavior, and then I can create and test a CP/M 3 image that uses more space.

It is sounding like maybe this new controller is not going to work well with MBR, even *if* the SDK contains code for it. It would make handling the "segments" on the host PC easier/safer, but it may not be practical to implement on the microcontroller. It also would not have the behavior of the old Z67-IDE+ segments, as you cannot access beyond the end of an MBR partition like you can with the segments.

To view this discussion on the web visit https://groups.google.com/d/msgid/sebhc/966643C6-FE10-42E3-BEBD-7226967D029B%40koyado.com.

Glenn Roberts

The Z67 uses the interface protocol defined in the MRX101D controller which was originally designed for Memorex 101 disk drives. This is what Norberto has emulated in his implementation. The interface specification is here

http://koyado.com/Heathkit/Z67-IDE_files/MRX101D.controller.pdf

It uses sectors that are 256 bytes in size. the “Class 0” command (I/O) data structure (p. 14) allows 21 bits for sector addressing and three bits for logical unit number. Norberto’s controller maps the logical unit number to the CF (or soon to be SD) card, so LUN 0 is card 0, LUN 1 is card 1, etc. (though this could presumably be changed via software to refer to portions of the same SD/CF card). Each card can have 2**21 sectors which is 2,097,152 sectors or 538,870,912 bytes ( ½ Gig). So without software changes to the IDE+ software you’re constrained to ½ G per SD/CF card. the thumbwheel switches let you extend that space by remapping it within the card in 128 Mbyte chunks, but for any given thumbwheel setting your limited to the ½ Gig aligned to any given 128 Meg boundary specified by the switch settings.

If we were to partition the card into 8 logical units (rather than have the LUN refer to the physical card slot) you could support up to 4 G per card, however currently the LUN is used to select different cards. Not sure how hard it would be to redefine sector size (e.g. to 512, 1024, etc.) but that might be another option.

Frankly ½ Gig is so much space from an HDOS/CP/M concern I’m not sure it’s worth spending a lot of time on.

Now how much of the ½ Gig is usable at the OS level is a function of the drivers and BIOS definitions. The Heath/Zenith HDOS drivers used a 2-byte sector addressing scheme (presumably more efficient than juggling 3-byte entities). With 2 bytes you can address at most 65,536 sectors or 16 megabytes.. I believe the Quickstor and CP/M drivers are smarter and can access more.

Norberto implemented a special feature of his firmware that uses a control byte to access the full ½ Gig address space. I use this in my “jukebox” software to access a whole swath of space that’s “invisible” to HDOS otherwise.

To view this discussion on the web visit https://groups.google.com/d/msgid/sebhc/c8eaa81a-9f49-ff4d-9bb0-0de539aab325%40gmail.com.

Douglas Miller

right, I had neglected to consider the SASI protocol in

computations of usable space. CP/M 3's 512M per drive capacity

matches the SASI protocol max capacity per LUN, but not when you

put a bunch of "pseudo SASI drives" onto a single storage card

accessed via SASI.

The GIDE, and possible (direct) SDCard, interfaces should not have any such limitation.

Although, a 512M CP/M drive still has it's issues. Not least of

which, it probably needs an 8000-entry directory which would take

a long time to read on first access, let alone that that requires

a huge amount of directory HASH space (32K). Also, addressing that

much storage requires the use of fairly large allocation blocks,

so there is more wasted space (esp. for small files).

To view this discussion on the web visit https://groups.google.com/d/msgid/sebhc/004201d6c328%245c7f8ee0%24157eaca0%24%40gmail.com.

Steven Hirsch

> It may be better to just access the SDCard "raw", but I thought I'd ask. FYI,

> CP/M 3 does not have the 8M partition limitation, it can support a 256M drive

> (partition). It just seemed that getting out of the fixed-size segment might

> be worth exploring.

partitions. Limit is 512MB, I believe.

Norberto Collado

It may be better to just access the SDCard "raw", but I thought I'd ask. FYI, CP/M 3 does not have the 8M partition limitation, it can support a 256M drive (partition). It just seemed that getting out of the fixed-size segment might be worth exploring.

To view this discussion on the web visit https://groups.google.com/d/msgid/sebhc/90eef9c6-a44f-43a7-8fad-4c03c058617d%40gmail.com.

Kenneth L. Owen

Hi Norberto,

The Z67-IDE (and IDE+) use the switches for multisystem boots. Unless there is a problem with the root data, if a system fails to boot, you can select another one which will boot and now have a way to recover the one that quit working.

To view this discussion on the web visit https://groups.google.com/d/msgid/sebhc/20201125100411.1321cca37f09b4ab87c5049afdc8ceaa.37964701c5.wbe%40email09.godaddy.com.

Douglas Miller

I'm not proposing any major changes. I simply thought that using

MBR might make things easier. If not, then I think things should

stay the same.

To view this discussion on the web visit https://groups.google.com/d/msgid/sebhc/20201125100411.1321cca37f09b4ab87c5049afdc8ceaa.37964701c5.wbe%40email09.godaddy.com.

Norberto Collado

To view this discussion on the web visit https://groups.google.com/d/msgid/sebhc/1d07ebdb-2e31-135a-551b-b53497dcd0c4%40gmail.com.

Norberto Collado

Attached is latest Z67-SD PCB board. I made several changes based on feedback received and it looks better than before.

Thanks,

Norberto

From: "se...@googlegroups.com" <se...@googlegroups.com> on behalf of Norberto Collado <norberto...@koyado.com>

Reply-To: "se...@googlegroups.com" <se...@googlegroups.com>

Date: Wednesday, November 25, 2020 at 3:13 PM

To: "se...@googlegroups.com" <se...@googlegroups.com>

Subject: RE: [sebhc] New Z67-SD Controller

Thanks for the feedback!

To view this discussion on the web visit https://groups.google.com/d/msgid/sebhc/20201125161327.1321cca37f09b4ab87c5049afdc8ceaa.4faacec8e1.wbe%40email09.godaddy.com.

Joseph Travis

To view this discussion on the web visit https://groups.google.com/d/msgid/sebhc/78A0FBA4-9B9B-484F-A206-4F5513B6998E%40koyado.com.

Glenn Roberts

Joe: bottom line: this is a peripheral that works with both the H8 and H89!

Longer story:

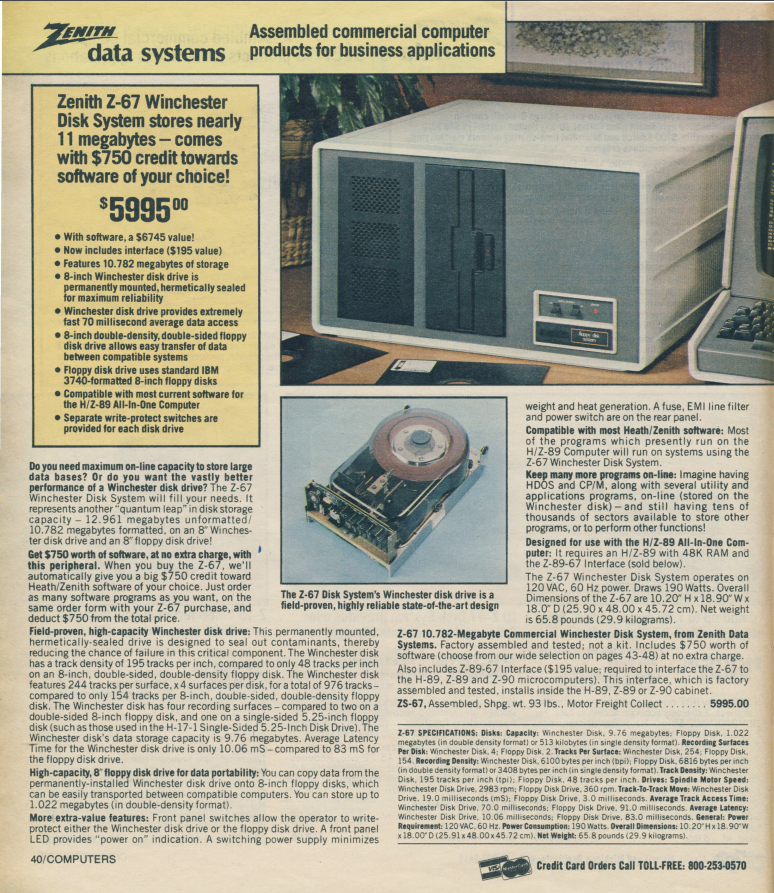

Norberto is updating the design for his “Z-67” emulator. The Z-67 was a large, heavy and expensive accessory for the H8/H89 that provided for an 8” floppy drive and an 11 meg hard (what they then called “Winchester”) drive. The Z-67 was actually shown in catalogs (see below, Spring/Summer 1982) primarily as an H89 accessory at the time, but it can be used with either the H8 or H89. Norberto reverse engineered the SASI protocols and implemented the same functionality on a single board. His first generation of the device was in fact built on a card that could fit in the H8 chassis, or could be mounted externally in a 5-1/4” drive bay. His second generation was smaller and mounts in a 3-1/2” bay. They connect to the controller card in the computer via a SASI ribbon cable. Both those versions rely on Compact Flash drives as the solid-state storage medium. CF devices are expensive and somewhat difficult to obtain so Norberto is moving to the more common Secure Digital (SD) card plus a simpler design with new display features as well.

To talk to the Z67-IDE device your computer needs a SASI controller card. Norberto designed a Z67 interface card for the ’89 in 2015 – looks like he may still have a few available…

http://koyado.com/Heathkit/H89-Z67.html

He has recently updated his design for the H8 interface board

http://koyado.com/Heathkit/H8-H17-H37-H67-USB.html

To view this discussion on the web visit https://groups.google.com/d/msgid/sebhc/CAGQDgBDdMRzGEPHxbeCm6bFzAE%2BVxA5_sMiAu80b5COrzvHMjw%40mail.gmail.com.

Douglas Miller

The terminology used here can be confusing. "Z67" might refer to

the SASI interface board, plugged into an H8 or H89 (different

boards). Or it might refer to the external cabinetry, power

supply, SASI controller, and harddisk. Or some combination of

those. Norberto (at al.) built a modern functional replacement for

the (now rare and/or obsolete) external components. This was the

Z67-IDE, then Z67-IDE+, and now (what I presume will be called)

the Z67-SDC.

The SASI interface board is really just a parallel port

specialized according to the SASI standard. The "SASI drives" are

really the combination of a SASI controller board (lots of

"smarts" - a CPU, firmware, etc) and one (or occasionally more)

harddisk drives. SASI is the predecessor of SCSI, and has the same

basic topology - very simple interface to the bus on computers

(initiators), complex controllers on the peripherals (targets),

high-level command structure to abstract-away hardware

differences.

In theory, the Z67-IDE(+) would work on any computer (non-Heathkit) that has a SASI interface. It replaces the fragile and difficult to repair/replace controller+harddisk combination.

To view this discussion on the web visit https://groups.google.com/d/msgid/sebhc/CAGQDgBDdMRzGEPHxbeCm6bFzAE%2BVxA5_sMiAu80b5COrzvHMjw%40mail.gmail.com.

Norberto Collado

WOW, $5999.00 back in the 80’s!!! Today’s price per CPI is $20,098.92. A lot of money.

Thanks Glenn on such great feedback.

Norberto

To view this discussion on the web visit https://groups.google.com/d/msgid/sebhc/069401d6c586%2477af8750%24670e95f0%24%40gmail.com.

Norberto Collado

SDC for “Secure Digital Card”? Yes, I can do that. Z-67 named was used to honor the Heath Z-67 external storage solution per add from Glenn’s previous email.

To view this discussion on the web visit https://groups.google.com/d/msgid/sebhc/a5b57294-184b-5ada-b9f7-fec0a417158d%40gmail.com.

Glenn Roberts

On Nov 28, 2020, at 2:32 PM, Norberto Collado <norberto...@koyado.com> wrote:

To view this discussion on the web visit https://groups.google.com/d/msgid/sebhc/595D40C1-396D-4BBB-A94E-5EAB6EB28063%40koyado.com.

Norberto Collado

To view this discussion on the web visit https://groups.google.com/d/msgid/sebhc/595D40C1-396D-4BBB-A94E-5EAB6EB28063%40koyado.com.

Norberto Collado

Douglas Miller

Hi Norberto,

That sounds reasonable. Are you going to emulate SASI with 256-byte sectors, or 512? With 256 the SASI protocol can only address 512M (with 512 can address 1G).

Either way, 1G segments seems fine, even if half of that is inaccessible. I don't don't how available 2G, 4G, 8G, or 16G cards are, but those might suffer a bit of a loss by the larger segmentation. I'm assuming you'll just provide fewer segments in those cases, same as the CF card? I suspect we don't need to squeeze every byte out of a card, and that no one will likely need 16 segments, let alone 100.

To view this discussion on the web visit https://groups.google.com/d/msgid/sebhc/20201203203435.1321cca37f09b4ab87c5049afdc8ceaa.8e73e88111.wbe%40email09.godaddy.com.

Norberto Collado

To view this discussion on the web visit https://groups.google.com/d/msgid/sebhc/133e1293-6467-5b99-acd4-13b42c6d9fa8%40gmail.com.

Douglas Miller

Just had a "hair-brained" thought... might be good to set that 256/512 switch well-recessed, so it can't be accidentally flipped. Or maybe even do something to embed the 256/512 setting on the media itself. I can't imagine a case where you'd want to flip that switch once you've put OS images on the disk. The drivers will need to know the sector size, I think. I can't imagine being able to switch on-the-fly without reinitializing software.

To view this discussion on the web visit https://groups.google.com/d/msgid/sebhc/20201204111257.1321cca37f09b4ab87c5049afdc8ceaa.11230f3c63.wbe%40email09.godaddy.com.

Norberto Collado

Great feedback! I added an I2C NVRAM chip, so I can have that feature there.

NVRAM:

0x0000 = VD Settings (0-99)

0x0001 = 256/512 switch selection (0x00 = default = 256, 0x01 = 512 byte per sector.

0x……. = tbd (future expansion)

To view this discussion on the web visit https://groups.google.com/d/msgid/sebhc/1c85f08a-f729-8cf6-9d1a-700322690436%40gmail.com.

Glenn Roberts

I presume there will be port I/O access to read/write the NVRAM? (e.g.to query the sector size and other parameters)…

To view this discussion on the web visit https://groups.google.com/d/msgid/sebhc/4AAB092D-BBE2-4846-AEA2-CE7FB9D52437%40koyado.com.

Douglas Miller

Actually, I was thinking that the 256/512 setting needed to be on

the (each) SDCard. For example one could make an image based on

512-byte sectoring and one for 256, whichever one is insert then

gets the right setting. Otherwise, one has to label the card and

remember to flip the switch.

But, that would require some hi-jinks to figure out where on the

card to put it. So, not sure if it is practical. But, if it's

worth pursuing perhaps the group can come up with a nice solution.

To view this discussion on the web visit https://groups.google.com/d/msgid/sebhc/4AAB092D-BBE2-4846-AEA2-CE7FB9D52437%40koyado.com.

Norberto Collado

-------- Original Message --------

Subject: RE: [sebhc] New Z67-SD Controller

From: "Glenn Roberts" <glenn.f...@gmail.com>

Date: Fri, December 04, 2020 6:27 pm

To: <se...@googlegroups.com>

I presume there will be port I/O access to read/write the NVRAM? (e.g.to query the sector size and other parameters)…

To view this discussion on the web visit https://groups.google.com/d/msgid/sebhc/047d01d6caae%2434564e80%249d02eb80%24%40gmail.com.

Norberto Collado

NVRAM:0x0000 = VD Settings (0-99)

0x0001 = SD#0 - 256 or 512 selection (0x02 = default = 256, 0x05 = 512 byte per sector.0x0002 = SD#1 - 256 or 512 selection (0x02 = default = 256, 0x05 = 512 byte per sector.To do this automatically by reading the SD card, a one sector will need to be reserved with such setting on the card; perhaps the last sector on a 1GB range, reserved and protected with the "2" or "5" value preloaded. I think this is overkill.Using the NVRAM setup will be easier. Also I'm adding the LCD and I can display NVRAM settings such as; "SD0: 256, SD1: 512....", so the user knows which slot to use. Or we can use a HDOS/CPM SASI commands to display NVRAM settings, or use the serial port to query the configuration as well.

Thanks,Norberto

-------- Original Message --------

Subject: Re: [sebhc] New Z67-SD Controller

From: Douglas Miller <durga...@gmail.com>

Date: Fri, December 04, 2020 6:36 pm

To: se...@googlegroups.com

Actually, I was thinking that the 256/512 setting needed to be on the (each) SDCard. For example one could make an image based on 512-byte sectoring and one for 256, whichever one is insert then gets the right setting. Otherwise, one has to label the card and remember to flip the switch.

But, that would require some hi-jinks to figure out where on the card to put it. So, not sure if it is practical. But, if it's worth pursuing perhaps the group can come up with a nice solution.

On 12/4/20 7:27 PM, Norberto Collado wrote:

To view this discussion on the web visit https://groups.google.com/d/msgid/sebhc/17c425f2-0973-5f91-c614-2acafdfe9025%40gmail.com.

Norberto Collado

Updates on the Z67-SDC controller development:

HDOS

- Boots HDOS at 2/4 MHz

- Under OS it will switch fine to 8MHz and 10 MHZ.

CP/M-CP/M3:

- Boots CP/M at 2/4 MHz

- Under OS it fails to run at 8MHz and 10MHz.

- CP/M hangs @2MHZ under stress test after +1hr. It is a random issue that I cannot find, as under HDOS it works fine.

- Cannot continue development until this issue is resolved as it is a random issue that takes +1hr to surface.

- I did check for stack corruption, but it is fine.

- Interrupts are disabled when failure occurs.

- The issue is that it reads the command from the H8, then it changes to the correct SASI Phase, and then it dies before sending any data to the H8. The watchdog kicks in and resets the Z37-SDC controller.

- Once in the fail state, I can manually assert “REQ”, and when the watchdog kicks in, it recovers as it sends a check condition to retry command and continues to run the stress test until it fails again.

- Slow Debug Process - WIP…

Added features:

- Jukebox support to use .5GB of storage space. Thanks to Terry for finding that it was using only half of a .5GB.

- Inquiry Command – Thanks to Terry for his support on this. It is still evolving.

- 256/512 sector transfers. Selection is control by using the serial port and changes saved into the EEPROM.

- SPI bus clock frequency selection. Selection is done under serial port and changes saved into the EEPROM.

Thanks,

Norberto

To view this discussion on the web visit https://groups.google.com/d/msgid/sebhc/20201204231504.1321cca37f09b4ab87c5049afdc8ceaa.485fcfa6c3.wbe%40email09.godaddy.com.

George Farris

Douglas Miller

MMS CP/M 3 images are built for the full 64K space, I don't think Norberto has the experience to run GENCPM and change that.

I'm curious, what would leaving extra space at the top of memory

give us?

To view this discussion on the web visit https://groups.google.com/d/msgid/sebhc/fd887e7104388394aafa8590c2c0f1c4f9e39bae.camel%40gmsys.com.

George Farris

To view this discussion on the web visit https://groups.google.com/d/msgid/sebhc/8fbf456a-aaa9-11cd-a0e7-08a47c58ceb5%40gmail.com.

Douglas Miller

The problem Norberto is chasing is some timing issue inside the Z67-SDC. There is no problem on the Z67-IDE or (presumably) a Z67 with standard SASI drive. The OS does not crash in any of these cases.

To view this discussion on the web visit https://groups.google.com/d/msgid/sebhc/1ebd24243e2b6d5fcc45277d8e553bac6f850f1e.camel%40gmsys.com.

Norberto Collado

I think is time to revive the Z67-SDC controller. I have been thinking for a while (since March 28, 2021) in trying to understand the timing issue on the Z67-SDC board. I decided to add an 74AHCT123 to one of clocks as the HW is pulsing one of the clocks too fast and the H8 somehow misses it as it never replies that it was received. The main benefit of this board is that it uses SD media and parts are very inexpensive.

Hopefully we will have this board working properly soon.

To view this discussion on the web visit https://groups.google.com/d/msgid/sebhc/15b0a4ac-54fd-02e9-dd28-042ffd5c6e14%40gmail.com.

Glenn Roberts

I still have my 1.1 version of the original IDE board – 12 years old now! A classic! A redesign/update would be good and will keep things going for another 10 or more years!

- Glenn

To view this discussion on the web visit https://groups.google.com/d/msgid/sebhc/5F0FC4F4-7532-480C-BD4C-89DAC79822A7%40koyado.com.

norberto.collado koyado.com

Sent: Monday, March 28, 2022 5:29 AM

To: se...@googlegroups.com <se...@googlegroups.com>

norberto.collado koyado.com

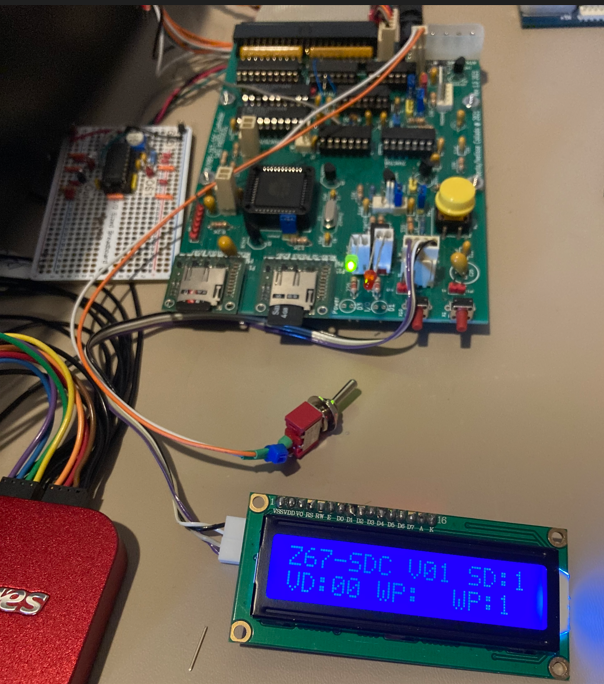

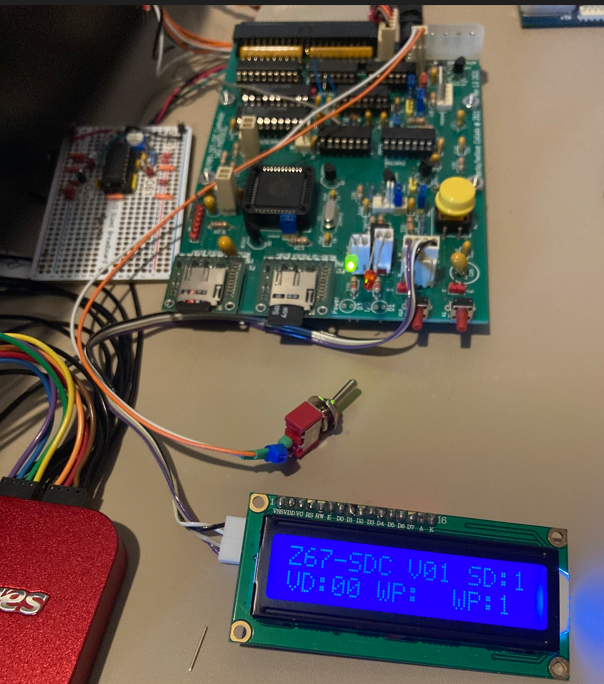

After a year, finally I was able to run the Z67-SDc at 2/4/8/10 MHz at the HDOS OS level. The timing issue was related to the signal /ACK. I was pulsing such signal at 1us. With Terry S. help, he created a small board to adjust such signal timing. Today I did made additional HW changes to the board created by Terry and adjusted the /ACK clock to 35ns. Finally this fix allowed me to boot HDOS without any issues and run at 10MHz.

I have been stressing the SD card all day and so far no issues reading or writing to it. Very stable.

Here is a picture of the working board. As I’m scrapping such design for a better one, at least I got it to work, and a lot learned when trying to emulate an SCSI IC in software.

Thanks

Norberto

To view this discussion on the web visit https://groups.google.com/d/msgid/sebhc/5F0FC4F4-7532-480C-BD4C-89DAC79822A7%40koyado.com.

Glenn Roberts

On Jul 25, 2022, at 12:14 AM, norberto.collado koyado.com <norberto...@koyado.com> wrote:

After a year, finally I was able to run the Z67-SDc at 2/4/8/10 MHz at the HDOS OS level. The timing issue was related to the signal /ACK. I was pulsing such signal at 1us. With Terry S. help, he created a small board to adjust such signal timing. Today I did made additional HW changes to the board created by Terry and adjusted the /ACK clock to 35ns. Finally this fix allowed me to boot HDOS without any issues and run at 10MHz.

I have been stressing the SD card all day and so far no issues reading or writing to it. Very stable.

Here is a picture of the working board. As I’m scrapping such design for a better one, at least I got it to work, and a lot learned when trying to emulate an SCSI IC in software.

To view this discussion on the web visit https://groups.google.com/d/msgid/sebhc/SN6PR01MB3855654C1C6F79877FBA719BF7959%40SN6PR01MB3855.prod.exchangelabs.com.