NI card clock terminals, migration from Atticus/Cicero to labscript

159 views

Skip to first unread message

Alexander Chuang

May 25, 2022, 5:17:18 PM5/25/22

to the labscript suite

Hi everyone,

I'm a grad student at MIT, and we're excited to port our experiment to run on labscript. We are currently having some trouble with the differences between the architecture of labscript and Atticus/Cicero.

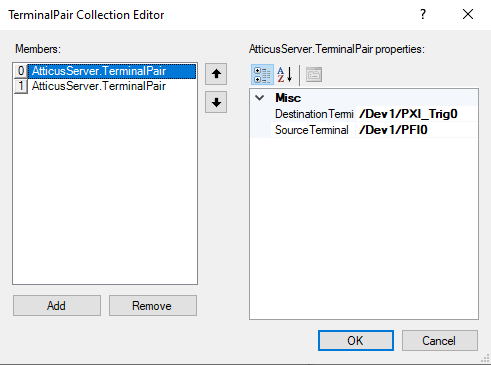

We have 4 NI PXI cards (dev1, dev2, dev3, and dev4) housed in a PXI chassis. The pseudoclock signal is physically connected to only PFI0 on dev1, while the other cards (2, 3 and 4) receive the pseudoclock signal through the shared PXI bus (PXI_Trig0). As I understand, the routing of the signal from dev1/PFI0 to PXI_Trig0 is a "software wired" connection set up through Atticus. This is shown in the screenshot.

I'm a grad student at MIT, and we're excited to port our experiment to run on labscript. We are currently having some trouble with the differences between the architecture of labscript and Atticus/Cicero.

We have 4 NI PXI cards (dev1, dev2, dev3, and dev4) housed in a PXI chassis. The pseudoclock signal is physically connected to only PFI0 on dev1, while the other cards (2, 3 and 4) receive the pseudoclock signal through the shared PXI bus (PXI_Trig0). As I understand, the routing of the signal from dev1/PFI0 to PXI_Trig0 is a "software wired" connection set up through Atticus. This is shown in the screenshot.

I see in the discussion https://groups.google.com/g/labscriptsuite/c/4ctKDJoNysA/m/Vht6A2JaCAAJ that this functionality is not immediately supported in labscript. However, it seems the NI infrastructure for distributing the pseudoclock signal through the chassis via a shared bus exists. For us, it would be a waste and redundant to add new hardware, just so we can tell labscript that each card has a clock terminal dev{idx}/PFI0.

To test labscript on our experiment, we run a short script, with a prawnblaster clockline connected to dev1/PFI0. We run into two distinct problems, depending on how we configure the connection table. If we configure the table as:

"""

NI_PXI6713(name='ni_analog_card_1',

...,

clock_terminal='/Dev1/PFI0',

MAX_name='Dev1')

NI_PXI6713(name='ni_analog_card_2',

...,

clock_terminal='/Dev2/PXI_Trig0',

MAX_name='Dev2')

NI_PXI6534(name='ni_analog_card_3',

...,

clock_terminal='/Dev3/PXI_Trig0',

MAX_name='Dev3')

NI_PXI6534(name='ni_analog_card_4',

...,

clock_terminal='/Dev4/PXI_Trig0',

MAX_name='Dev4')

"""

after running a shot we encounter the error message in the blacs tabs for cards 2, 3, and 4, but not for card 1, suggesting that the connection table has not properly configured cards 2, 3, 4 for receiving pseudoclock triggers:

"""

Traceback (most recent call last):

File "C:\Users\Fermi1\AppData\Local\conda\conda\envs\labscript_py38\lib\site-packages\labscript_devices\NI_DAQmx\blacs_workers.py", line 357, in transition_to_manual

task.WaitUntilTaskDone(1)

File "<string>", line 3, in WaitUntilTaskDone

File "<string>", line 2, in function

File "C:\Users\Fermi1\AppData\Local\conda\conda\envs\labscript_py38\lib\site-packages\PyDAQmx\DAQmxFunctions.py", line 62, in mafunction

raise exception_class(errBuff.value.decode("utf-8"), f.__name__)

PyDAQmx.DAQmxFunctions.WaitUntilDoneDoesNotIndicateDoneError: Wait Until Done did not indicate that the task was done within the specified timeout.

Increase the timeout, check the program, and make sure connections for external timing and triggering are in place.

Task Name: _unnamedTask<1>

Status Code: -200560

in function DAQmxWaitUntilTaskDone.

Fatal exception in main process - Mon May 23, 14:35:43 :

Traceback (most recent call last):

File "C:\Users\Fermi1\AppData\Local\conda\conda\envs\labscript_py38\lib\site-packages\blacs\tab_base_classes.py", line 837, in mainloop

next_yield = inmain(generator.send,results)

File "C:\Users\Fermi1\AppData\Local\conda\conda\envs\labscript_py38\lib\site-packages\qtutils\invoke_in_main.py", line 88, in inmain

return get_inmain_result(_in_main_later(fn, False, *args, **kwargs))

File "C:\Users\Fermi1\AppData\Local\conda\conda\envs\labscript_py38\lib\site-packages\qtutils\invoke_in_main.py", line 150, in get_inmain_result

raise value.with_traceback(traceback)

File "C:\Users\Fermi1\AppData\Local\conda\conda\envs\labscript_py38\lib\site-packages\qtutils\invoke_in_main.py", line 46, in event

result = event.fn(*event.args, **event.kwargs)

File "C:\Users\Fermi1\AppData\Local\conda\conda\envs\labscript_py38\lib\site-packages\blacs\device_base_class.py", line 677, in transition_to_manual

raise Exception('Could not transition to manual. You must restart this device to continue')

Exception: Could not transition to manual. You must restart this device to continue

"""

On the other hand, if I instead pass 'Dev1/PFI0' as the clock_terminal to cards 2, 3, and 4, i.e.

"""

NI_PXI6713(name='ni_analog_card_1',

...,

clock_terminal='/Dev1/PFI0',

MAX_name='Dev1')

NI_PXI6713(name='ni_analog_card_2',

...,

clock_terminal='/Dev1/PFI0',

MAX_name='Dev2')

etc.

"""

we do not encounter any errors in blacs after running a shot, but the NI cards do not appear to have outputted as desired.

In short, we'd be super grateful to hear any ideas on how we can use the PXI shared bus to trigger different cards in the same chassis, and/or if any folks have successfully transitioned from Cicero/Atticus to labscript without changing the hardware setup.

Ian B. Spielman

May 25, 2022, 5:31:02 PM5/25/22

to 'Philip Starkey' via the labscript suite, Alexander Chuang

Dear Alexander,

For years in our labview based implementation we had NI cards mirroring a PFI input used to trigger other devices as a sort of clone pseudoclock signal. This sounds similar to the routing you are describing.

As long as the NI-MAX shows the ports you are listing as an option things should work (look for a mirror clock option in the NI labscript code as a legacy of this). Personally I very strongly suggest you send each of your devices its own pseudoclock on its own PFI port. This has the major benefit of decreasing the amount of data sent to devices that are not actually being updated.

Right now we are using pulseblaster cards to give us 24 (almost) independent pseudocloks, but if I were to set things up fresh I would make a swarm of prawnblasters instead.

— Ian

Ian B. Spielman

Fellow, Joint Quantum Institute

National Institute of Standards and Technology and the University of Maryland

----- WEB -----

http://ultracold.jqi.umd.edu

----- EMAIL -----

spie...@jqi.umd.edu

----- ZOOM -----

https://umd.zoom.us/j/7984811536

----- PHONE -----

(301) 246-2482

----- MAIL -----

UMD:

2207 Computer & Space Sciences Bldg.

College Park, MD 20742

NIST:

100 Bureau Drive, Stop 8424

Gaithersburg, MD 20899-8424 USA

----- OFFICE -----

UMD: Physical Sciences Complex, Room 2153

NIST: Building 216, Room B131

> On May 25, 2022, at 17:17, Alexander Chuang <alex.ch...@gmail.com> wrote:

>

>

> Hi everyone,

>

> I'm a grad student at MIT, and we're excited to port our experiment to run on labscript. We are currently having some trouble with the differences between the architecture of labscript and Atticus/Cicero.

>

> We have 4 NI PXI cards (dev1, dev2, dev3, and dev4) housed in a PXI chassis. The pseudoclock signal is physically connected to only PFI0 on dev1, while the other cards (2, 3 and 4) receive the pseudoclock signal through the shared PXI bus (PXI_Trig0). As I understand, the routing of the signal from dev1/PFI0 to PXI_Trig0 is a "software wired" connection set up through Atticus. This is shown in the screenshot.

>

> --

> You received this message because you are subscribed to the Google Groups "the labscript suite" group.

> To unsubscribe from this group and stop receiving emails from it, send an email to labscriptsuit...@googlegroups.com.

> To view this discussion on the web, visit https://groups.google.com/d/msgid/labscriptsuite/014a6fa9-acd6-4da9-b97a-d8acbeec2b80n%40googlegroups.com.

> <atticusScreenshot.png>

For years in our labview based implementation we had NI cards mirroring a PFI input used to trigger other devices as a sort of clone pseudoclock signal. This sounds similar to the routing you are describing.

As long as the NI-MAX shows the ports you are listing as an option things should work (look for a mirror clock option in the NI labscript code as a legacy of this). Personally I very strongly suggest you send each of your devices its own pseudoclock on its own PFI port. This has the major benefit of decreasing the amount of data sent to devices that are not actually being updated.

Right now we are using pulseblaster cards to give us 24 (almost) independent pseudocloks, but if I were to set things up fresh I would make a swarm of prawnblasters instead.

— Ian

Ian B. Spielman

Fellow, Joint Quantum Institute

National Institute of Standards and Technology and the University of Maryland

----- WEB -----

http://ultracold.jqi.umd.edu

----- EMAIL -----

spie...@jqi.umd.edu

----- ZOOM -----

https://umd.zoom.us/j/7984811536

----- PHONE -----

(301) 246-2482

----- MAIL -----

UMD:

2207 Computer & Space Sciences Bldg.

College Park, MD 20742

NIST:

100 Bureau Drive, Stop 8424

Gaithersburg, MD 20899-8424 USA

----- OFFICE -----

UMD: Physical Sciences Complex, Room 2153

NIST: Building 216, Room B131

> On May 25, 2022, at 17:17, Alexander Chuang <alex.ch...@gmail.com> wrote:

>

>

> Hi everyone,

>

> I'm a grad student at MIT, and we're excited to port our experiment to run on labscript. We are currently having some trouble with the differences between the architecture of labscript and Atticus/Cicero.

>

> We have 4 NI PXI cards (dev1, dev2, dev3, and dev4) housed in a PXI chassis. The pseudoclock signal is physically connected to only PFI0 on dev1, while the other cards (2, 3 and 4) receive the pseudoclock signal through the shared PXI bus (PXI_Trig0). As I understand, the routing of the signal from dev1/PFI0 to PXI_Trig0 is a "software wired" connection set up through Atticus. This is shown in the screenshot.

>

> You received this message because you are subscribed to the Google Groups "the labscript suite" group.

> To unsubscribe from this group and stop receiving emails from it, send an email to labscriptsuit...@googlegroups.com.

> To view this discussion on the web, visit https://groups.google.com/d/msgid/labscriptsuite/014a6fa9-acd6-4da9-b97a-d8acbeec2b80n%40googlegroups.com.

> <atticusScreenshot.png>

Alexander Chuang

May 26, 2022, 4:58:07 PM5/26/22

to the labscript suite

Dear Ian,

MAX_name='Dev1')

NI_PXI6713(name='ni_analog_card_2',

...,

Thank you for the kind and helpful suggestions! The legacy feature worked exactly as specified, and we will definitely consider the prawnblaster swarm as we do the migration.

To close this issue, here is a snippet of a working connection table, in which outputs from cards 2-4 are all synchronized with card 1 via the shared bus line PXI_Trig0.

"""

NI_PXI6713(name='ni_analog_card_1',

...,

clock_terminal='/Dev1/PFI0',

NI_PXI6713(name='ni_analog_card_1',

...,

clock_terminal='/Dev1/PFI0',

clock_mirror_terminal='/Dev1/PXI_Trig0',

MAX_name='Dev1')

NI_PXI6713(name='ni_analog_card_2',

...,

clock_terminal='/Dev1/PXI_Trig0',

MAX_name='Dev2')

NI_PXI6534(name='ni_digital_card_3',

...,

clock_terminal='/Dev1/PXI_Trig0',

MAX_name='Dev3')

NI_PXI6534(name='ni_digital_card_4',

...,

clock_terminal='/Dev1/PXI_Trig0',

MAX_name='Dev4')

"""

MAX_name='Dev2')

NI_PXI6534(name='ni_digital_card_3',

...,

clock_terminal='/Dev1/PXI_Trig0',

MAX_name='Dev3')

NI_PXI6534(name='ni_digital_card_4',

...,

clock_terminal='/Dev1/PXI_Trig0',

MAX_name='Dev4')

"""

-- Alex

Reply all

Reply to author

Forward

0 new messages