Bone VDD_3V3EXP Disable Issues

Andrew Bradford

turning off should disable U8 linear regulator causing VDD_3V3EXP to

turn off.

It doesn't.

Disabling LDO3 in the TPS65217 causes VDD_3V3A to drop to approximately

2.4 V. This is not low enough to disable the U8 linear regulator's

enable pin. Further, disabling LDO4 after this only causes VDD_3V3A to

drop to approximately 1.2 V. Again, this is not enough to disable U8

linear regulator's enable pin.

I've tested on an A3 and an A6 bone.

I realize there's grave impacts to disabling LDO3 or LDO4, ie: much of

the board won't work any more although the ARM core and DDR will still

be operating. That's OK for my experiments.

How can I turn off VDD_3V3EXP from software without completely turning

off all rails on the TPS65217? Is it possible?

I'm trying to do this in order to debug an issue we see with a custom

cape at power down when running on 3.7 V lithium battery. With our cape

attached, VDD_3V3EXP latches on even when the rest of the BeagleBone is

powered off. This is due to SYS_5V staying present due to the battery

and U8 linear regulator not powering down before the latch action

occurs. The TPS65217 and AM3359 are both in the proper states, I can

boot due to power button press once in the OFF state (defined by the

TPS65217 data sheet). But keeping VDD_3V3EXP running will ruin the

battery life while in the OFF state.

On the cape, we pull up to VDD_3V3EXP for things like MMC/SD and I2C.

I believe this is part of the problem as there may be power back feeding

through the pull-ups enough to cause the latch situation. But we

believe we're following the recommended pull-up strategy documented in

the Bone SRM.

Has any one else seen issues like this when attempting to enter the

TPS65217 OFF state with capes attached that use pull-ups to VDD_3V3EXP

while running on 3.7 V lithium battery power? If so, what capes work?

Yes, I realize this is quite a corner case. Sadly, it's an important

one for me.

Thanks,

Andrew

Gerald Coley

Andrew Bradford

Gerald Coley <ger...@beagleboard.org> wrote:

> You are correct. This is something we just ran into yesterday and we

> are looking at a solution. The solution is being tested and will not

> be something that shows up in the near future, but hopefully soon. It

> MAY be something that could be done with a wire mod, but it is too

> early to tell. Should know more by Monday.

Even if the wire mod is complex, it'd be great if you could share it.

anderse...@gmail.com

Gerald Coley

Gerald Coley

Thanks for replying.

Yes I have seen that note. And when the battery is not connected the VDD_3V3A does shutdown, but not when a battery is connected (A6 version). When I measure the voltage on VDD_3V3A after the ‘shutdown’, it is about 2.4V (it is 3.3V when ON). Is there a path for leakage back to that node that is keeping the voltage up?

The registers in the PMIC are the same for both board versions. I have not changed them from what comes with the BBB.

I used this method to test the shutdown:

Uboot example:

- Boot to the uboot prompt by pressing any key before the kernel boots

- Set the PMIC i2c status register to turn OFF when EN line goes down. (i2c, memory write, device 24, address A, value 0x80)

> i2c mw 24 A 80- Set the memory base to the RTC registers

> base 44e3e000- Enable PWR_ENABLE_EN bit (memory write, offset address 98, value in hex 0x00010000)

> mw 98 10000- Enable ALARM2 interrupt once (memory write, offset address 48, value in hex 0x00000010)

> mw 48 10- Copy over RTC current time to ALARM2 times for hour/day/month/year (memory copy, from address 8, to address 88, 4 times)

> cp 8 88 4- This next part is where it gets slightly more complicated because you are going to manually set the ALARM2 minutes to one or two minutes after the current time.

- Read the current seconds, minutes. This is easy to manually do because they are in BCD and not in hex. (memory display, address zero, 2 times)

> md 0 2

44e3e000: 00000008 00000011 (8 seconds, 11 minutes)- Write to the ALARM2 minutes (seconds should already be zero) (memory write, address 84, value 0x00000012)

> mw 84 12 (12 minutes)- Wait until the current time catches up to the ALARM2 time and the system will power down. If you took too long doing step 7.2 and the time has already passed, just do step 7.2 again.

- While you're waiting you can keep checking the current time ( this will show all 6 fields, second, minute, hour, day, month, year)

> md 0 6- And if you think you have passed your ALARM2 time you can compare above results with ALARM2 time. If so, go to step 7.2. If you went onto a new hour, you might have to start from step 6.

> md 80 6Thanks,

Brad

Brad Andersen

Did you look here?

Gerald Coley

The SYS_5V bus has the Battery supply, approx. 3.8V

How can I make sure “all rails are actually turned off via SW”?

I’ll go through the procedure and measure all the voltages and report back.

Brad Andersen

The SYS_5V bus has the Battery supply, approx. 3.8V

How can I make sure “all rails are actually turned off via SW”?

I’ll go through the procedure and measure all the voltages and report back.

Sent: Thursday, December 19, 2013 7:43 AM

To: Brad Andersen

Brad Andersen

was confused about the dates and board versions you referred to.

Brad

-----Original Message-----

From: Andrew Bradford [mailto:and...@bradfordembedded.com]

Sent: Thursday, December 19, 2013 8:50 AM

To: Brad Andersen

Cc: 'Gerald Coley'; beagl...@googlegroups.com

Subject: Re: [beagleboard] Bone VDD_3V3EXP Disable Issues

> The SYS_5V bus has the Battery supply, approx. 3.8V

>

>

>

> How can I make sure "all rails are actually turned off via SW"?

>

>

>

> I'll go through the procedure and measure all the voltages and report

back.

If so, does your cape have any pull-up resistors on it?

Are we talking about white or black bones? I've lost that in this

conversation. My original experiments were all with white bones.

Thanks,

Andrew

PS: Please keep me CC'ed, I'm no longer subscribed to the list.

> 2. Set the PMIC i2c status register to turn OFF when EN line goes down.

>> i2c mw 24 A 80

>> base 44e3e000

> 4. Enable PWR_ENABLE_EN bit (memory write, offset address 98, value in

>> mw 98 10000

>> mw 48 10

>> cp 8 88 4

> after the current time.

>

> 2

> times)

>> md 0 2

> 44e3e000: 00000008 00000011 (8 seconds, 11 minutes)

>> mw 84 12 (12 minutes)

>

> time has already passed, just do step 7.2 again.

>

>> md 0 6

Andrew Bradford

>

>

>

> How can I make sure "all rails are actually turned off via SW"?

>

>

>

> I'll go through the procedure and measure all the voltages and report back.

If so, does your cape have any pull-up resistors on it?

Are we talking about white or black bones? I've lost that in this

conversation. My original experiments were all with white bones.

Thanks,

Andrew

PS: Please keep me CC'ed, I'm no longer subscribed to the list.

> Sent: Thursday, December 19, 2013 7:43 AM

> To: Brad Andersen

> Cc: beagl...@googlegroups.com; Andrew Bradford

> Subject: Re: [beagleboard] Bone VDD_3V3EXP Disable Issues

>

>

>

> The change only affected when the 3V3B rail was enabled by enabling it with

> the 3V3A rail. So, I can't see how they are related. Both LDOs are powered

> by the same SYS_5V bus.

>

>

>

> What is the level of the SYS_5V bus?

>

>

>

> The battery in this case is now supplying all of the LDOs and switchers. So

> I am thinking that maybe we need to make sure all rails are actually tuned

> off via SW.

>

>

>

> Gerald

>

>

>

>

>

> On Thu, Dec 19, 2013 at 9:26 AM, Brad Andersen <br...@lite-check.com> wrote:

>

> Thanks for replying.

>

>

>

> Yes I have seen that note. And when the battery is not connected the

> VDD_3V3A does shutdown, but not when a battery is connected (A6 version).

> When I measure the voltage on VDD_3V3A after the 'shutdown', it is about

> 2.4V (it is 3.3V when ON). Is there a path for leakage back to that node

> that is keeping the voltage up?

>

>

>

> The registers in the PMIC are the same for both board versions. I have not

> changed them from what comes with the BBB.

>

>

>

> I used this method to test the shutdown:

>

> Uboot example:

>

> 2. Set the PMIC i2c status register to turn OFF when EN line goes down.

>> i2c mw 24 A 80

>> base 44e3e000

> 4. Enable PWR_ENABLE_EN bit (memory write, offset address 98, value in

>> mw 98 10000

>> mw 48 10

>> cp 8 88 4

> the current time.

>

> times)

>> md 0 2

> 44e3e000: 00000008 00000011 (8 seconds, 11 minutes)

>> mw 84 12 (12 minutes)

>

> already passed, just do step 7.2 again.

>

>> md 0 6

Brad Andersen

Ok, here’s what I did:

No cape

Debug serial connected to desktop computer

1. Connect battery as designed

a. Batt+ to TP5

b. Batt+ to TP6

c. 10k between TP7 and TP8

d. Gnd to TP8

2. Connect +5V to power plug

3. Let BBB boot up

4. Login

5. Disconnect +5V

6. Dump PMIC registers (in order) (same for both boards)

a. 0xE2

b. 0x3E

c. 0

d. 0

e. 0xB1

f. 0x80

g. 0xB2

h. 0x01

i. 0

j. 0

k. 0x80

l. 0

m. 0x7F

n. 0x0C

o. 0x18

p. 0x02

q. 0x09

r. 0x06

s. 0x09

t. 0x38

u. 0x26

v. 0x3F

w. 0x7F

x. 0

y. 0x03

z. 0x15

aa. 0x5F

bb. 0x32

cc. 0x40

dd. 0x20

ee. 0

7. Shutdown –r now

8. Boot to Uboot prompt

9. “i2c mw 24 a 80” (set PMIC status register to turn OFF when PMIC_POWER_EN goes down)

10. “base 44e3e000”

11. “mw 98 10000”

12. “mw 48 10”

13. “cp 8 88 4”

14. “md 8 4”

15. “md 88 4” to check that the data transferred

16. “md 0 2”

17. “mw 84 xx”, time in future for Alarm2 to act

18. Wait for the shutdown

19. Measure voltages:

a. A6:

i. Vbatt = 4.03

ii. SYS_5V = 4.00

iii. VDD_5V = 0

iv. VDD_3V3B = 3.39

v. VDD_3V3A = 2.27

vi. VDDS_DDR = 0

vii. VDD_MPU = 0

viii. VDD_CORE = 0

ix. VDD_1V8 = 0.16

x. VRTC = 0.16

xi. VDD_3V3AUX = 0.16

b. A5C

i. Vbatt = 4.03

ii. SYS_5V = 4.03

iii. VDD_5V = 0

iv. VDD_3V3B = 0

v. VDD_3V3A = 0

vi. VDDS_DDR = 0

vii. VDD_MPU = 0

viii. VDD_CORE = 0

ix. VDD_1V8 = 0

x. VRTC = 0

xi. VDD_3V3AUX = 0

So those are my results. Any thoughts?

Brad Andersen

Darren McInnes

Terry

John Syn

Reply-To: "beagl...@googlegroups.com" <beagl...@googlegroups.com>

Date: Thursday, June 26, 2014 at 1:01 PM

To: "beagl...@googlegroups.com" <beagl...@googlegroups.com>

Cc: <and...@bradfordembedded.com>

Subject: [beagleboard] Re: Bone VDD_3V3EXP Disable Issues

Does anyone know if there is a software solution to this issue? I haven't seen any changes in the recent hardware revisions to address this. We are currently planning on deploying a couple of dozen BBB and I would prefer not having to make hardware mods.

Terry

On Thursday, January 30, 2014 12:34:51 PM UTC-5, Brad Andersen wrote:An update:For the A6 (Beaglebone Black) version, I connected U4 pin 1 (enable) back to VDD_3V3AUX (same as A5C). It now shuts down correctly while on battery. This was verified on two A6 BBB.The mystery is what causes the VDD_3V3A to hang up on the A6 version when shutting down while on battery.

--

For more options, visit http://beagleboard.org/discuss

---

You received this message because you are subscribed to the Google Groups "BeagleBoard" group.

To unsubscribe from this group and stop receiving emails from it, send an email to beagleboard...@googlegroups.com.

For more options, visit https://groups.google.com/d/optout.

JohnP

jjpit...@gmail.com

Matthijs van Duin

I've marked the PMIC sequencer "strobes" with vertical dashed lines, partially cut away when irrelevant or visually interfering with the signal plots. Unless noted otherwise, the interval between strobes is 1 ms.

As I mentioned, in off-state SYS is tied to BAT, and when DC-powered they hover around 1V for some reason (they'll drop if you try to drain power from either, but once you stop they bounce back to 1V). All regulated supplies are off. Once the PMIC has detected a wakeup event, it connects SYS to the DC power supply, asserts the wakeup signal, and the sequencer powers up the "always-on" supplies:

- strobe 15: LDO1 (rtc, vdds)

- strobe 14: unused

- strobe 1: DCDC1 (ddr)

- strobe 2: LDO3 (1v8)

- [5 ms delay]

- strobe 3: LDO2 (3v3aux = power led)

- strobe 4: LDO4 (3v3a, enables 3v3b)

- strobe 5: DCDC2 (mpu), DCDC3 (core)

- strobe 6: unused

- strobe 7: unused

Andrew Bradford

> To illustrate all this, let's stare at some pretty pictures.

>

> Here's a capture of various power terminals during boot and shutdown

> while

> on DC power (click to zoom):

>

> I've marked the PMIC sequencer "strobes" with vertical dashed lines,

> partially cut away when irrelevant or visually interfering with the

> signal

> plots. Unless noted otherwise, the interval between strobes is 1 ms.

>

> As I mentioned, in off-state SYS is tied to BAT, and when DC-powered they

> hover around 1V for some reason (they'll drop if you try to drain power

> from either, but once you stop they bounce back to 1V). All regulated

> supplies are off. Once the PMIC has detected a wakeup event, it connects

> SYS to the DC power supply, asserts the wakeup signal, and the sequencer

> powers up the "always-on" supplies:

>

>

> - strobe 14: unused

> The AM335x RTC asserts PW_EN and once debounced by the PMIC (~50 ms) the

> sequencer completes the power-on sequence:

>

>

> - strobe 2: LDO3 (1v8)

> - [5 ms delay]

> - strobe 3: LDO2 (3v3aux = power led)

> - strobe 4: LDO4 (3v3a, enables 3v3b)

> - strobe 5: DCDC2 (mpu), DCDC3 (core)

> - strobe 6: unused

> - strobe 7: unused

> Meanwhile, since BATMON isn't connected to BAT, the PMIC doesn't really

> get

> what's going on there. It seems to attempt to charge it for a while, then

> gives up, and later BAT somehow manages to drop below 0V and stay there

> (behaviour is quite different if BATMON is connected to BAT, in which

> case

> it's pulsed a few times then drops to about 0.2V - 0.4V, apparently

> depending on system load).

>

> When reentering off-state the PMIC shuts down the supplies in reverse

> order, with 1 ms between strobes 1 and 14. Strobe 7 is relevant this time

> because it marks when shutdown is initiated, and as a result SYS is

> disconnected from DC power and connects to BAT, which immediately shoots

> up

> shutdown.

> About 20 ms after it was supposed to, it finally begins to drop to zero

> while SYS, now unloaded and heavily supported by fat capacitors, begins

> its

> long and slow journey back towards the 1V.

>

> For comparison, the same plot but now powered at 3.6V through BAT (using

> a

> variable power supply).

>

> When BAT was powered up, SYS started tracking it once it reached 1V (hmm,

> sounds familiar), but the PMIC initially remains in off-state. The boot

> and

> shutdown are essentially the same, except SYS follows BAT continuously.

> As

> a result, once 3v3b is turned on, it remains on until power to BAT is

> cut.

>

>

> Bottom line: if you want to run on battery power, this is a serious

> problem. You'll need to keep the PMIC in active-state, though you can

> minimize power by commanding the ethernet phy and hdmi framer to power

> themselves down, and then enter a deepsleep mode. Alternatively, you'd

> need

> to patch the hardware, or have an external circuit detect this situation

> (3v3b on while 1v8_adc off) and disconnect the battery to resolve it.

My initial work was on BBW back in 2012 (prior to BBB release).

It sounds like BBB has similar issues to BBW with running on battery but

that the issues are slightly different.

I'm not subscribed to this list any longer so please keep me in CC.

Thanks!

-Andrew

Matthijs van Duin

You seem to be talking about the BBB, correct?

My initial work was on BBW back in 2012 (prior to BBB release).

It sounds like BBB has similar issues to BBW with running on battery but

that the issues are slightly different.

Matthijs van Duin

Your original question is actually very easy to answer

Andrew Bradford

line) and then wire U8 pin 5 to the PWR_LED net on page 2 of the

schematic, then the U8 LDO will shutdown correctly when on battery.

This fix was incorporated into BBB but apparently there are other

problems, too.

This is the only mod required to fix my original problem. No fancy

software needed.

Thanks,

Andrew

Matthijs van Duin

If you take a BBW and cut the trace coming from U8 pin 5 (the LDO enable

line) and then wire U8 pin 5 to the PWR_LED net on page 2 of the

schematic, then the U8 LDO will shutdown correctly when on battery.

- strobe 15: LDO1 (rtc)

- strobe 1: DCDC1 (vdds, 1v8, ddr)

- [5 ms delay]

- strobe 2: LDO2 (power led)

- strobe 3: LDO3 (3v3a, enables 3v3exp)

- strobe 4: LDO4 (3v3b)

This fix was incorporated into BBB but apparently there are other problems, too.

Andrew Bradford

On 04/29/2015 04:12 PM, Matthijs van Duin wrote:

> On Wednesday, 29 April 2015 20:18:51 UTC+2, Andrew Bradford wrote:

>>

>> If you take a BBW and cut the trace coming from U8 pin 5 (the LDO enable

>> line) and then wire U8 pin 5 to the PWR_LED net on page 2 of the

>> schematic, then the U8 LDO will shutdown correctly when on battery.

>>

>

> It will shut down.

>

> So, the BBW has a slightly different power scheme, including a different

> variant of the PMIC which affects timing and use of strobes. For reference,

> the relevant changes are:

>

>

> and

>

> - strobe 1: DCDC1 (vdds, 1v8, ddr)

> - [5 ms delay]

> - strobe 2: LDO2 (power led)

> - strobe 3: LDO3 (3v3a, enables 3v3exp)

> - strobe 4: LDO4 (3v3b)

I'm sure wonky power up and down timing is not helping the silicon.

For reference, I've not seen any failure of the am335x with this rework

when using a custom cape at my previous job. That's not saying there

isn't damage, just that I didn't see any. We had built up probably 200

BBW+cape systems. The custom cape used the 3V3EXP as an enable for

cape-side power converters, so that likely added a slight delay to the

cape actually starting and may mitigate some of the issue you're

pointing out.

Thanks,

Andrew

Matthijs van Duin

For reference, I've not seen any failure of the am335x with this rework

when using a custom cape at my previous job. That's not saying there

isn't damage, just that I didn't see any.

- 2× 4.75k for am335x boot mode (EMU0, EMU1)

- 11× 10k for eMMC

- 7× 10k for SD card

- 1× 10k for HDMI irq

- 4× 1.5k for ethernet (MDIO and phy mode select)

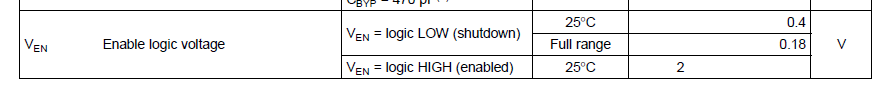

- 0.50 V (BBW regulator)

- 0.40 V (BBB regulator, 25 ͏°C)

- 0.18 V (BBB regulator, whole temperature range)

Matthijs van Duin

I've captured the shutdown sequence on DC versus BAT power in more detail

Max

Matthijs van Duin

Did you try any change in the EN pin of U4 (enable signal of 3V3B)?

I'm about to try SYS_RESETn (PMIC_PGOOD after U16), but I'm concerned about the 20ms turn on delay (plus 10ms due to the RC).The other option is to go back to use 3V3AUX, and add a 1k load resistor to reduce the discharge time.

Maximiliano O. Sonnaillon

Matthijs van Duin

I was considering that one because it's a 3.3V logic signal. PGOOD is a 1.8V signal and the EN pin of U4 has a minimum of 2V to consider it high.

my cape (it's actually more like a motherboard).

The reason I'm investigating these PMIC details is that I'm using a custom BBB for am industrial application, and we had a couple boards (BBB and custom one) fail. I recently found warnings in new BBBs to avoid "damage in the board".https://groups.google.com/forum/#!topic/beaglebone/CKuTbHepHYE

Matthijs van Duin

I will probably have to add an extra buffer to have PGOOD in 3.3V level

Heh, it's a pity U3 is an inverter rather than a buffer... it's currently not actually used (hardware reset is not enabled in eMMC), it's located at the top of the PCB (where you can also find PGOOD) while its output is available via R162 on the bottom of the PCB (where you'd need the enable signal for the regulator), and since its existing input and output connect to pins which are high-Z/don't-care by default you wouldn't even need to disconnect those.